A Multi-Processor System on Chip Architecture for Real Time Remote Sensing Data Processing

A Multi-Processor System on Chip Architecture for Real Time Remote Sensing Data Processing. Presenter: Dr. Alejandro Castillo Atoche. 2011/07/25. IGARSS’11. Outline. Introduction Previous Work MPSoC via the HW/SW Co-design Case Study: RBR Algorithms Algorithm Analysis

A Multi-Processor System on Chip Architecture for Real Time Remote Sensing Data Processing

E N D

Presentation Transcript

A Multi-Processor System on Chip Architecture for Real Time Remote Sensing Data Processing Presenter: Dr. Alejandro Castillo Atoche 2011/07/25 IGARSS’11 School of Engineering, AutonomousUniversityof Yucatan, Merida, Mexico.

Outline • Introduction • Previous Work • MPSoC via the HW/SW Co-design • Case Study: RBR Algorithms • Algorithm Analysis • Network on Chip (NoC)-based Accelerator • Integration in a Co-design scheme • New Perspective: Network of FPGA-VLSI architectures • Hardware Implementation Results • Performance Analysis • Conclusions School of Engineering, AutonomousUniversityof Yucatan, Merida, Mexico.

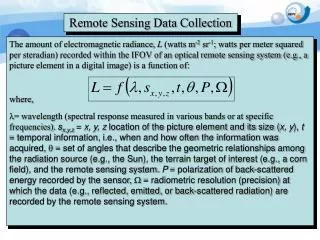

Introduction: Radar Imagery, Facts • The initial problem of this proposition for the Geospatial RS imagery consist in to solve the ill-conditioned inverse spatial spectrum pattern (SSP) estimation problem with model uncertainties via the Bayesian minimum risk (BMR) estimation strategy. • In previous works, alternatives of MPSoC propositions have been developed but without systolic arrays techniques or Network on a Chip structures. School of Engineering, AutonomousUniversityof Yucatan, Merida, Mexico.

Introduction: HW implementation, Facts • Why Multiprocessor System on a Chip? Because MPSoCs are single-chip multiprocessor designed for real time signal processing applications. • Why Network on a Chip Accelerators? Networks-on-chips (NoCs) are multiprocessor interconnection networks designed to achieved real time SP. Avoids Bottlenecks in HW/SW co-designs. School of Engineering, AutonomousUniversityof Yucatan, Merida, Mexico.

MOTIVATION • To efficiently conceptualize and implement an architecture with the aggregation of parallel computing and systolic array mapping techniques in a novel network on a chip (NoC) accelerator scheme via the HW/SW co-design paradigm. School of Engineering, AutonomousUniversityof Yucatan, Merida, Mexico.

CONTRIBUTIONS: • First, a high-speed robust Bayesian regularization hardware accelerator for the real-time enhancement of the large scale Geospatial imagery is designed. • Second, the use of High Performance Computing techniques in an efficient architecture based on Network on a Chip (NoC) is also developed. School of Engineering, AutonomousUniversityof Yucatan, Merida, Mexico.

Algorithmic ref. Implementation School of Engineering, AutonomousUniversityof Yucatan, Merida, Mexico.

Algorithmic ref. Implementation School of Engineering, AutonomousUniversityof Yucatan, Merida, Mexico.

Algorithmic ref. Implementation School of Engineering, AutonomousUniversityof Yucatan, Merida, Mexico.

Partitioning Stage School of Engineering, AutonomousUniversityof Yucatan, Merida, Mexico.

NoC oriented structure of the proposed coprocessors (a) Robust SS vector School of Engineering, AutonomousUniversityof Yucatan, Merida, Mexico.

NoC oriented structure of the proposed coprocessors • (b) RBR estimator School of Engineering, AutonomousUniversityof Yucatan, Merida, Mexico.

Aggregation of parallel computing techniques a[i,j] c[i,j] b[i-1, j] b[i,j] a[i,j-1] 3-D Dependance Graph (DG) Application for (tile=0, tile< L, tile++){ Linear Schedule: set of parallel and uniformely spaced hyperplanes. for (i=0, i< m, i++){ for (j=0, j< n, j++){ for (k=0, k< r, k++){ a(i,j,k)=a(i,j-1,k); b(i,j,k)=b(i-1,j,k); c(i,j,k)=c(i,j,k-1) + a(i,j,k)*b(i,j,k); SFG Projection } } } } School of Engineering, AutonomousUniversityof Yucatan, Merida, Mexico.

Tiling technique Large-Scale Real-World Image Fixed-Size SystolicArray School of Engineering, AutonomousUniversityof Yucatan, Merida, Mexico.

Tiling technique (1,2) (2,1) Large-Scale Real-World Image Fixed-Size SystolicArray School of Engineering, AutonomousUniversityof Yucatan, Merida, Mexico.

Fixed-Sized NoC-PAs-based Robust SS vector co-processor • Stage1: School of Engineering, AutonomousUniversityof Yucatan, Merida, Mexico.

Fixed-Sized NoC-PAs-based Robust SS vector co-processor • Stage2: School of Engineering, AutonomousUniversityof Yucatan, Merida, Mexico.

Fixed-Sized NoC-PAs-based Robust SS vector co-processor • Stage3: School of Engineering, AutonomousUniversityof Yucatan, Merida, Mexico.

Fixed-Sized NoC-PAs-based RBR estimator co-processor School of Engineering, AutonomousUniversityof Yucatan, Merida, Mexico.

New Perspective:VLSI-FPGA Platforms • Novel VLSI-FPGA platform represents a new perspective for real time processing of newer RS applications. School of Engineering, AutonomousUniversityof Yucatan, Merida, Mexico.

VLSI-FPGA Platform School of Engineering, AutonomousUniversityof Yucatan, Merida, Mexico.

Performance Analysis: FPGA School of Engineering, AutonomousUniversityof Yucatan, Merida, Mexico.

Performance Analysis: FPGA School of Engineering, AutonomousUniversityof Yucatan, Merida, Mexico.

Conclusions • The implementation results of the proposed NoC-PA-oriented architecture helps to drastically reduce the overall processing time of the RBR algorithm. In fact, the presented architecture is efficiently implemented in MPSoC mode in spite of employing systems based on traditional DSPs or PC-Clusters platforms . • The implementation of the RBR algorithm using the proposed architecture takes only 1.26 seconds for the large-scale RS image reconstruction in contrast to 19.7 seconds required with the C++ implementation. Thus, the achieved processing time is approximately 16 times less than the corresponding processing time with the conventional C++ PC-based implementation. School of Engineering, AutonomousUniversityof Yucatan, Merida, Mexico.

Recent Selected Journal Papers • A. Castillo Atoche, D. Torres, Yuriy V. Shkvarko, “Towards Real Time Implementation of Reconstructive Signal Processing Algorithms Using Systolic Arrays Coprocessors”, JOURNAL OF SYSTEMS ARCHITECTURE (JSA), Edit. ELSEVIER, Volume 56, Issue 8, August 2010, Pages 327-339, ISSN: 1383-7621, doi:10.1016/j.sysarc.2010.05.004. JCR. • A. Castillo Atoche, D. Torres, Yuriy V. Shkvarko, “Descriptive Regularization-Based Hardware/Software Co-Design for Real-Time Enhanced Imaging in Uncertain Remote Sensing Environment”, EURASIP JOURNAL ON ADVANCES IN SIGNAL PROCESSING (JASP), Edit. HINDAWI, Volume 2010, 31 pages, 2010. ISSN: 1687-6172, e-ISSN: 1687-6180, doi:10.1155/ASP. JCR. • Yuriy V. Shkvarko, A. Castillo Atoche, D. Torres, “Near Real Time Enhancement of Geospatial Imagery via Systolic Implementation of Neural Network-Adapted Convex Regularization Techniques”, JOURNAL OF PATTERN RECOGNITION LETTERS, Edit. ELSEVIER, 2011. JCR. In Press School of Engineering, AutonomousUniversityof Yucatan, Merida, Mexico.

Thanks for your attention. • Dr. Alejandro Castillo Atoche • Email: acastill@uady.mx School of Engineering, AutonomousUniversityof Yucatan, Merida, Mexico.