Understanding Data Acquisition System for N-XYTER

240 likes | 401 Vues

Understanding Data Acquisition System for N-XYTER. Set-up Requirements. Measurement of time, energy and position Data acquisition speed ~ 1Gbps Input Clock ~ 250MHz Input channels ~ 1024 or higher Data - 8-bit parallel after flash ADC ADC – Flash type 8-bit (MAX-106 600MSPS)

Understanding Data Acquisition System for N-XYTER

E N D

Presentation Transcript

Set-up Requirements • Measurement of time, energy and position • Data acquisition speed ~ 1Gbps • Input Clock ~ 250MHz • Input channels ~ 1024 or higher • Data - 8-bit parallel after flash ADC • ADC – Flash type 8-bit (MAX-106 600MSPS) • Time stamp, channel-ID and status signals 32 bit(8-bit parallel x 4 packet)

Data packet for time-stamp channel-id and status signals Differential analog output in N-XYTER

Some parameters form CBM • Each channel detects autonomously all hits • An absolute time stamp, precise to a fraction of the sampling period, is associated with each hit • All hits are shipped to the next layer (usually concentrators) • Association of hits with events done later using time correlation • Typical Parameters: • with few 1% occupancy and 107 interaction rate: • some 100 kHz channel hit rate • few MByte/sec per channel • whole CBM detector: 1 Tbyte/

Basic Idea for Readout for 4-chip FEE board Readout controller (ROC) FEE-board 1Gbps FOL Serial fiber optic peripheral

Basic n-XYTER Readout Chain Front-EndBoard Detector Read-OutController Active BufferBoard FEB ROC ABB Tag data XYTER Tag data XYTER MGT MGT ADC data FPGA ADC FPGA Tag data XYTER SFP MGT MGT Tag data XYTER control clock Bond orcableconnection up to 8 N-XYTER1024 ch. LVDSsignalcable 2.5 Gbpsopticallink 1-4 lanePCIeinterface

Scalable n-XYTER Readout Chain Front-EndBoard Detector Read-OutController Data CombinerBoard FEB ROC DCB Tag data XYTER Tag data XYTER MGT SFP SFP MGT MGT ADC data FPGA ADC FPGA Tag data XYTER SFP MGT Tag data SFP MGT XYTER control clock to otherROC's to ABB

Some Configurations Minimal Configuration PC Detector FEB ROC ABB Expandable Configuration Data Combiner Board Detector FEB ROC Detector FEB ROC PC DCB ABB Detector FEB ROC Detector FEB ROC

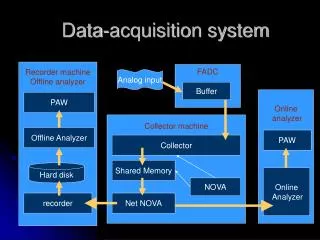

OLDER READOUT EXPERIENCE MANAS MANAS MARC MANAS MANAS ADC ADC FEE BOARD LVTTL DATA and CONTROL lines TRANSLATOR BOARD LVDS LINK DAQ

Proposed idea to have the test set-up SIU used in CROCUS DAQ ROC Exixting CROCUS DAQ can be used as ABB card just to make the ROC card with FEE board 1Gbps link External board with FPGA and Buffer FEE

Proposed N-XYTER Readout scheme NXYTER NXYTER NXYTER NXYTER ADC FEE BOARD ASIC based ROC LVDS CONTROL and DATA lines To other FEE boards DCB with 10 Gbps SFP link OFC link DAQ

Readout controller (ROC) board • Raw data and memory management • Data acquisition and processing (data tagging). • Data transfer at 1Gbps by Multi gigabyte Tran-receiver (MGT) and then send via serial fiber optic link of 1Gbps • I2C driver for N-XYTER configuration and slow control.

Control bus to N-XYTER To FOL 1Gbps link

N-XYTER Chip configuration • All internal bias, thresholds and DAC references are programmable through I2C slow control @ 100Kbps by total 46 resisters. • ROC board is to be built to program and to control above mentioned control resisters and FPGA program can be changed by JTAG port. • Next slide shows proposed scheme for N-XYTER configuration and control through I2C bus.

I2C Programming Scheme I2C_ID0 I2C_ID6 I2C_ID0 I2C_ID6 I2C_ID0 I2C_ID6 I2C_ID0 I2C_ID6 N-XYTER N-XYTER N-XYTER N-XYTER SDA FPGA SLC

Algorithm • Configuration data to be entered form computer to FPGA via RS-232 interface and stored in IIC EPROM. • On start or restart of the system configuration data to be transferred to the N-XYTER through IIC bus. • Status resister can be read back from N-XYTER through RS-232 port.

Computer Control • For configuration of the XYTER to set the threshold values and control words, a LINUX based platform is used in the PC. The software in the PC extend the facility to configure all the control Words and the same can be down loaded to the EEPROM on the ROC board through RS232 link . The EEPROM is connected through a IIC bus to FPGA and configure the XYTER with SOFTWARE CONTROL from the PC • The ROCKET IO/ GTP provide data at 1GBPS in the serial format • The standard Desk Top PC has a limitation to acquire data at 1GBPS so a SERVER is required to handle the High-speed data @1gbps from the ROC board through light link • JTAG PROGRAMMING • The FPGA selected are nonvolatile and reprogrammable. However for programming the JTAG port is available at the board . • We require XILINX ISE software and JTAG Cable for development and downloading the software.

RS-232 UART-BLOCK Center Control-Block BUS-Controller Block GTP-Controller I/O and Contol Bus to N-Xyter SIU SERVER MEMORY

Active Buffer Board V-4 MGT basedoptical link This board is under construction and is expected soon. V-4 MGT basedPCI-Express interface(4 lanes)