Flip Chip/Bumping Process at VTT

Flip Chip/Bumping Process at VTT. By Jaakko Salonen (jaakko.salonen@vtt.fi). Last modified March 16, 2007. VTT's Flip Chip Process: Overview. Flip Chip Bonding With Solder Bumps. Area array type interconnecting technology is ideal for hybridizing pixel sensors with readout chips.

Flip Chip/Bumping Process at VTT

E N D

Presentation Transcript

Flip Chip/Bumping Processat VTT By Jaakko Salonen (jaakko.salonen@vtt.fi) Last modified March 16, 2007

VTT's Flip Chip Process: Overview

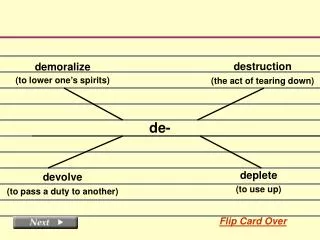

Flip Chip Bonding With Solder Bumps Area array type interconnecting technology is ideal for hybridizing pixel sensors with readout chips. Solder bumping is done by electroplating for whole wafers. The wafers are then diced, and the individual chips are flip chip bonded together. Sensor chip, typically hi-res (1 1 1) silicon. Typical bump diameter: 20...30 um Typical bump pitch: 50...200 um Bump/pixel count per ROC: ~2,000...65,000 Readout chips, 0.25-um CMOS, typically 1 to 10 ROC’s per sensor chip.

Main Process Steps 1. Incoming Inspection & Wafer Cleaning. 2. Sputtering of Field Metals. 3. Photolithography Step. 4. Electroplating of UBM & Solder. 5. Stripping of Photoresist. 6. Etching of Field Metal 2. 7. Etching of Field Metal 1. 8. Solder Reflow. 9. Thinning of Readout Wafers (optional). 10. Dicing. 11. Flip Chip Bonding. Steps marked inredare done in a Class-10 clean room. Steps marked in blue are done in a Class 10,000 clean room.

Flip Chip Hybridization 1(4) Sensor & Readout wafers Sensor wafer Readout IC wafer

Flip Chip Hybridization 2(4) Bumping process (at wafer level) Sensor wafer Solderable pads Readout IC wafer Solder bumps

Flip Chip Hybridization 3(4) Dicing & chip pick-up Detector wafer Readout IC wafer

Flip Chip Hybridization 4(4) Flip chip bonding (chip-by-chip) Sensor chip Readout chip Readout chip Hybridized sensor/readout (detector) assembly Sensor chip Sensor & readout chips

VTT's Flip Chip Process: Step by Step

Incoming Inspection Zeiss Axiotron 2 Microscope Visual incoming inspection of wafers is done before bumping process. After inspection, wafers are cleaned using liquid solvents and ultrasound. Dirt particle on customer's readout wafer

Sputtering of Field Metals Von Ardenne CS730S Sputterer Sputtered Ti-W/Cu (40 nm/700 nm) layer is used as field metal for electroplating. Light in situ sputter etching step is used to remove native oxide from Al contact pads. Von Ardenne CS730S is used for 4", 5", and 6" wafers. TEL Eclipse Mk. IV is used for 8" wafers. TEL Eclipse Mk. IV Sputterer

Photolithography Suss MA200 & MA6 Mask Aligners Patterned 18-mm thick photoresist is used to define the bump sites on the wafers. Suss MicroTEC ACS200 Automated Coating System is used to coat wafers with photoresist. Suss MicroTEC MA6 Mask Aligner is used to expose 4", 5", and 6" wafers. Suss MicroTEC MA200 Mask Aligner is used to expose 8" wafers. Suss ACS200 PR coating system

Electroplating Wet bench for electroplating Nickel is first electroplated in the holes in the photoresist Solder is then electroplated on top of the nickel. Essentially the same process is used for both the sensor and the readout side; only the volume of the solder is different. Wafer holder for electroplating

Stripping of Photoresist After electroplating, photoresist is stripped away using solvents and ultrasound on automated wet bench.

Etching of Field Metals The field metals, which short-circuited the bump sites to one another during electroplating, are removed by wet etching.

Solder Reflow ATV SRO-704 Reflow Oven • ATV SRO-704 Reflow Oven is used for solder bump reflow. • Formic acid ambient reduces oxides on bump surfaces. Bumps after reflow

Wafer Thinning Strasbaugh 7AF Back Grinder Strasbaugh 6DS-SP CMP Strasbaugh 7AF Intelligent Grinder is used for back grinding. Strasbaugh 6DS-SP CMP Planarizer is used for CMP polishing. A layer of protective tape is used to protect the bumps and the front side of the wafer. 200 mm Si wafer back ground & polished to thickness of 150 mm

Dicing Wafers are laminated on tape/ tape frames for dicing Disco DFD651 Dicing Saw Disco DFD651 Dicing Saw is used for dicing. DFD651 in action

Flip Chip Bonding Close-up of bonded chips Suss FC150 Flip Chip Bonders Flip chip [tack] bonding is performed on two Suss MicroTEC FC150 Flip Chip Bonders. A post-tack bonding 'assembly reflow' for self-alignment is done in the ATV SRO-704 Reflow Oven in a formic acid ambient. Suss FC150 in use

Summary • An overview of VTT's flip chip process was given. • Electroplating is used to deposit solder on wafers at sites defined by photoresist. • Readout wafers can be optionally thinned after bumping. • All process steps are performed in house. • 4", 5", 6", and 8" wafers can be processed.

VTT Technical Research Centre of Finland Tietotie 3, Otaniemi, Espoo, Finland The End. Thank you for your attention.