Segment Descriptor

Segment Descriptor. Segment Descriptor. Segments are areas of memory defined by a programmer and can be a code, data or stack segment.

Segment Descriptor

E N D

Presentation Transcript

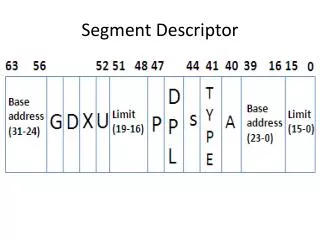

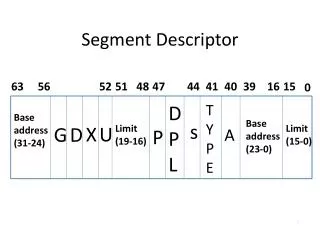

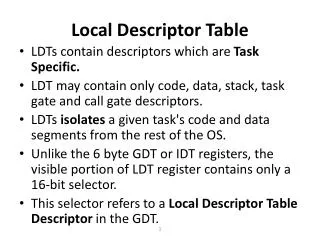

Segment Descriptor • Segments are areas of memory defined by a programmer and can be a code, data or stack segment. • In 80386 segments need not be all the same size and aligned. And segments need not be exactly 64 KB long, but we can define them to be any length from 1 byte to 4 GB. • In 80386 memory segmentation, it is not possible to use a 16-bit segment register to represent all the information related to segment. When multiple privilege levels and intertask protection are required a special structure called a segment descriptor is used.

Segment Descriptor • The description of a segment includes its base address, length, type, privilege level and some security information. • The lower base address is specified in bits 16 to 39 and upper 8 bits are specified in bits 56 to 63. • The lower 16 bits of segments limit are specified in 0-15 and the remaining 4 bits are specified in 48-51.

Non System Segment descriptors • Defines data, code, stack segments. • Used by both system and application programs. • S=1 in access right byte.

Non System Segment descriptors • P bit indicates whether segment is present in memory or not. P = 0 -> Segment is not present and P = 1-> Segment is present. • DPL: defines privilege level of the segment. Used to protect segment from low privilege caller.

Non System Segment descriptors • S: Used to distinguish between non system segment and system segment descriptors. • S = 1-> Non system segment descriptor. • E: Executable; Used to distinguish between data and code segments. E=0 -> Data segment including stack. E = 1 -> Code segment. • ED/C: Expand direction/conforming; When E=0, then this bit functions as ED, ED indicates whether the segment is data or stack. ED = 0 -> Data segment( access segment randomly). Offset address limit. ED = 1 -> Stack segment LIFO.

Non System Segment descriptors • When E =1, then this bit functions as C ( conforming) bit. Used to distinguish between conforming and nonconforming code segments. • C= 0 -> Non conforming code segment. • C = 1 -> Conforming code segment. • R/W Read/Write. When E= 0( data segment), then this bit functions as W bit. This bit indicates whether data segment is writable or not. • W = 0 -> data segment is not writable. W= 1 -> data segment is writable.

Non System Segment descriptors • When E =1 (code segment) then this bit functions as R bit. This bit indicates whether code segment is readable or not. R = 0 -> code segment is not readable and R = 1 -> code segment is readable. • A: Accessed; This bit indicates whether the segment is accessed or not. A= 1 -> Segment accessed. This bit is reset by OS periodically. A= 0 -> Segment not accessed

System Segment descriptor Type • All system descriptors are present in GDT while some system descriptors are present in LDTs. • Normally system segment descriptor are used by OS. • The value of S in right access byte is 0. • Their functions are fixed and specified by Intel. • The type of system descriptor is indicated by type field. • The system segment descriptors have no Accessed bit, instead the type field (3 bits) is now extended to 4 bits. • The system segment descriptors contain the information about tables (LDT), tasks(TSS) and gates (call gate, interrupt gate, task gate, trap gate) of the OS.

LDT descriptor (s=0, Type 2) • The LDT descriptors are present in the GDT. They contain the information about the LDT. • LDT contains the segment descriptors that are unique to a particular task. • The DPL field of the descriptor is ignored as this descriptor can only be accessed with a privilege level of 0. • Here type field =2 i.e. it specifies a LDT descriptor.

TSS (Task State Segment) Descriptors (s=0, Type 1, 3, 9 and B) • Whenever a computer is performing more than one tasks at a time it may also switch between these tasks. • The task may be a single program or a group of program. • When one task switches to another task , it stores all the necessary information required to restart the task where it was left. This information is called as the “ state of the task” • For storing the state of the task the 80386 processor uses a special segment called the “Task State Segment (TSS)”

TSS (Task State Segment) Descriptors (s=0, Type 1, 3, 9 and B) • The task segment is addressed with the help of TSS descriptor. It contains information about the location, size and privilege level of a TSS. • A TSS descriptor appears only in GDT and not in IDT or LDT. • The TSS consists the linkage field for the nest task that permits the nesting of the tasks.

TSS (Task State Segment) Descriptors (s=0, Type 1, 3, 9 and B) • B bit indicates whether task is busy or not. B=0 : Task is not busy B=1 : Task is busy

Gate descriptors (S=0, Type 4,5,6,7,C,F) • Whenever 4,5,6,7 is specified in type field it specifies a call gate, task gate, interrupt gate and trap gate respectively. • All fields are same as specified earlier except the word count, selector and offect. • The word count field specifies the number of parameters that are to be copied from caller’s stack to the called procedure’s stack.

Gate descriptors (S=0, Type 4,5,6,7,C,F) • Call gate are used to modified privilege levels. • Trap and interrupt gates are used in interrupt and exception handling. • The task gates are used in multitasking system

Protected Virtual Address Mode Physical address calculation in the protected virtual address mode

Protected Virtual Address Mode 1) PLs > Pldesc->access to segment allowed. 2)MMU checks__> Pdesc determine__> segpresent__>phymem. 3) exception load__>segmemreturn__> interrupted prog. 4) 1st & 2nd step satisfied MMU will add 16 bit offset.