Memory Organization

E N D

Presentation Transcript

Memory Organization Module IV

Elements of Cache Design • It includes: • Cache Addresses • Cache Size • Mapping Function • Replacement Algorithms • Write Policy • Line Size • Number of Caches

Cache Addresses • When virtual addresses are used, the system designers have two options to place the cache • between the processor and the MMU (Logical Cache) or • between the MMU and main memory (Physical Cache)

Logical Cache • It is also known as a virtual cache. • It stores data using virtual addresses. • The processor accesses cache directly, without going through MMU. • Advantage: It is faster than physical cache, because the cache can respond before the MMU performs an address translation.

Logical Cache • Disadvantage: • Most virtual memory systems supply each application with the same virtual memory address space(that starts at address 0). • Thus, the same virtual address in two different applications refers to two different physical addresses. • The cache memory must therefore be completely flushed with each application context switch, or • extra bits must be added to each line of the cache to identify which virtual address space this address refers to.

Physical Cache • It stores data using main memory physical addresses.

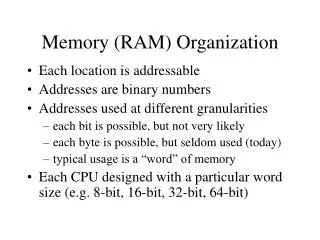

Cache Size • Size of the cache to be • small enough so that the overall average cost per bit is close to that of main memory alone and • large enough so that the overall average access time is close to that of the cache alone.

Mapping Function • Main memory and cache are both divided into same size blocks • It deals with how a cache with numerous entries search quickly and report a hit if a match is found. • Cache may be organized in different hardware configurations.

Cache Organization • The 3 main designs are: • Directly Mapped • Fully Associative & • Set Associative

Direct Mapped Cache • It uses a portion of incoming physical address to select an entry. • Suppose a cache has 27 = 128 lines, each with 16 bytes. • Suppose the memory has a 16-bit address and hence (216 = 64KB) address space. • Each memory line j maps to cache line j mod 128 and the memory address looks like:

Mapping Cache line size = 16 byte Cache Memory = 2KB No. of cache lines = 128 Main Memory = 64KB No of main memory lines = 64KB/16B = 216/24 = 212 =4096

Example • Suppose we want to read or write a byte at the address 357A • 357A(16) = 0011010101111010. • Tag = 6 • Line = 87 • Word = 10 • If line 87 in cache has tag 6, then data at 357A is in cache. • Else, a miss has occurred • Contents of cache line 87 is replaced by contents of memory line 001101010111 = 855

Simulation • Consider line size of 4 bytes • No. of cache memory lines is 8 and No. of main memory lines is 24

Simulation Main Memory Memory References: 2,7,15,22,17,16, 14,18,8,4,15,17 Cache

Simulation Main Memory Memory References: 2,7,15,22,17,16, 14,18,8,4,15,17 Cache 2 mod 8 =2 MISS !!!

Simulation Main Memory Memory References: 2,7,15,22,17,16, 14,18,8,4,15,17 Cache 7 mod 8 =7 MISS !!!

Simulation Main Memory Memory References: 2,7,15,22,17,16, 14,18,8,4,15,17 Cache 15 mod 8 =7 MISS !!!

Simulation Main Memory Memory References: 2,7,15,22,17,16, 14,18,8,4,15,17 Cache 22 mod 8 =6 MISS !!!

Simulation Main Memory Memory References: 2,7,15,22,17,16, 14,18,8,4,15,17 Cache 17 mod 8 =1 MISS !!!

Simulation Main Memory Memory References: 2,7,15,22,17,16, 14,18,8,4,15,17 Cache 16 mod 8 =0 MISS !!!

Simulation Main Memory Memory References: 2,7,15,22,17,16, 14,18,8,4,15,17 Cache 14mod 8 =6 MISS !!!

Simulation Main Memory Memory References: 2,7,15,22,17,16, 14,18,8,4,15,17 Cache 18mod 8 =2 MISS !!!

Simulation Main Memory Memory References: 2,7,15,22,17,16, 14,18,8,4,15,17 Cache 8mod 8 =0 MISS !!!

Simulation Main Memory Memory References: 2,7,15,22,17,16, 14,18,8,4,15,17 Cache 4mod 8 =4 MISS !!!

Simulation Main Memory Memory References: 2,7,15,22,17,16, 14,18,8,4,15,17 Cache 15mod 8 =7 HIT !!!

Simulation Main Memory Memory References: 2,7,15,22,17,16, 14,18,8,4,15,17 Cache 17mod 8 =1 HIT !!!

Fully Associative Cache • It allows main memory block to be placed anywhere in cache • It uses larger tags and does not use index. • Here the upper bits of incoming address is compared with every tag in cache. • This require more extensive hardware • But it is more flexible

Fully Associative Cache • Suppose a cache has 27 = 128 lines, each with 16 bytes. • Suppose the memory has a 16-bit address and hence (216 = 64KB) address space. • Each memory address looks like:

Example • Suppose we want to read or write a byte at the address 357A • 357A(16) = 0011010101111010. • Tag = 855 • Word = 10 • Tag 855 has to be searched in entire cache and if found then data at 357A is in cache. • Else, place contents of memory line 855 in the empty space in cache or apply LRU to replace.

Simulation • Consider line size of 4 bytes • No. of cache memory lines is 8 and No. of main memory lines is 24

Simulation Main Memory Memory References: 2,7,15,22,17,16, 14,18,8,4,15,18 Cache

Simulation Main Memory Memory References: 2,7,15,22,17,16, 14,18,8,4,15,18 Cache MISS !!!

Simulation Main Memory Memory References: 2,7,15,22,17,16, 14,18,8,4,15,18 Cache MISS !!!

Simulation Main Memory Memory References: 2,7,15,22,17,16, 14,18,8,4,15,18 Cache MISS !!!

Simulation Main Memory Memory References: 2,7,15,22,17,16, 14,18,8,4,15,18 Cache MISS !!!

Simulation Main Memory Memory References: 2,7,15,22,17,16, 14,18,8,4,15,18 Cache MISS !!!

Simulation Main Memory Memory References: 2,7,15,22,17,16, 14,18,8,4,15,18 Cache MISS !!!

Simulation Main Memory Memory References: 2,7,15,22,17,16, 14,18,8,4,15,18 Cache MISS !!!

Simulation Main Memory Memory References: 2,7,15,22,17,16, 14,18,8,4,15,18 Cache MISS !!!

Simulation Main Memory Memory References: 2,7,15,22,17,16, 14,18,8,4,15,18 Cache MISS !!!

Simulation Main Memory Memory References: 2,7,15,22,17,16, 14,18,8,4,15,18 Cache MISS !!!

Simulation Main Memory Memory References: 2,7,15,22,17,16, 14,18,8,4,15,18 Cache HIT !!!

![[Packet] My Memory Organization](https://cdn1.slideserve.com/1905829/packet-my-memory-organization-dt.jpg)