Sub- Nyquist Sampling Algorithm Implementation on Flex Rio

Sub- Nyquist Sampling Algorithm Implementation on Flex Rio. High Speed Digital Systems Lab. By : Genady Paikin , Ariel Tsror . Supervisors : Inna Rivkin , Rolf Hilgendorf. Agenda :. Project overview Goals Learning Process Hardware Sampling stage CTF module DSP module Gantt Chart.

Sub- Nyquist Sampling Algorithm Implementation on Flex Rio

E N D

Presentation Transcript

Sub-Nyquist Sampling Algorithm Implementation on Flex Rio High Speed Digital Systems Lab By : GenadyPaikin, Ariel Tsror. Supervisors : Inna Rivkin, Rolf Hilgendorf.

Agenda : • Project overview • Goals • Learning Process • Hardware • Sampling stage • CTF module • DSP module • Gantt Chart

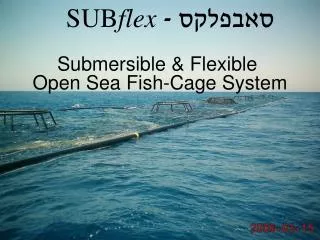

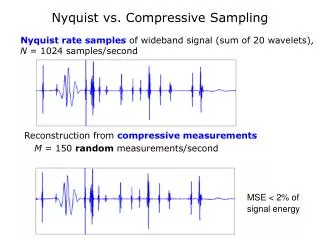

Project Overview • The project is part of the Sub-Nyquist sampling and reconstruction card. • Our goal is to implement 2 units – CTF & DSP, on FlexRio FPGA cards under NI LabView environment. • The unit also includes the Xampling sampling card And the Expand unit.

Goals : • Main goal – implementing CTF & DSP on FPGA’s under NI LabView environment using VHDL, Full integration, running full system at real time. • Optimization : • Latency. • Resources. • Minimize reconstruction errors.

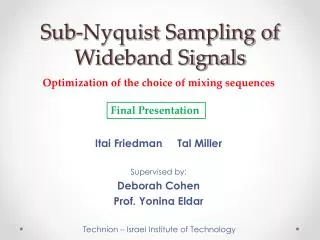

Hardware : • NI chassis with 4* FlexRio FPGA modules • FlexRio : • Model : NI PXIe 7965R • Bus : PXI Express • FPGA : Virtex-5 SX95T (Xilinx) • FPGA memory : 8,784 Kbits • Onboard Memory : 512MB • FPGA Slices : 14,720 • FPGA DSP Slices : 640 • A/D. • Xampling sampling card. * Expand, DSP, CTF, Reconstruction

Learning Process : • Learning process composed of 2 independent processes : • Algorithm : • System main concept. • Sampling stage (Xampling and Expand). • CTF module. • DSP module (inc. SCD). • LabView : • LabView main concepts. • FPGA under LabView. • Integration. • Implementing Basic unit as training. • Reading matrix from file to memory on FlexRio FPGA using LabView environment.

High Level Architecture : Xampling

Sampling stage : • The sampling stage contain two units • Xampling sampling card. • Expand. 12X20.8 Mhz digital 4X62.5 Mhz digital Xampling A/D 62.5 Mhz (250 1:4 decim.) Expand 1:3 Analog in

CTF module : • Task : Detects the Support of x(t) and forward it to DSP unit. • Triggered at : • Initiation. • SCD interrupt. • The unit based on OMP (Orthogonal Matching Pursuit) algoritm.

Block Diagram : A A MP Supp y[n] frame calculation Q

DSP module : • Task: Reconstructs the signal from the samples. • The unit receives the samples from the memory (latency fifo), matrix A from the memory, and signal support from the CTF unit. • The support and samples are coordinated by the latency fifo. • The unit performs pseudo-inverse of matrix A (calculates As) using the signal support, that is received from the CTF. • Finally the unit multiply the delayed signal with matrix As.

DSP module : DSP Matrix A (from memory) Pseudo Inverse As+ Signal support (from CTF) Reconstructed signal Signal’s sample (from memory) Multiplication

SCD module : • Task: Detects if there is a change of the signal support. • The unit uses the signal energy to decide if the CTF needs to recalculate the signal support. Recalculate support (to CTF) Signal’s sample (from expand) Support Change Detector