Announcements

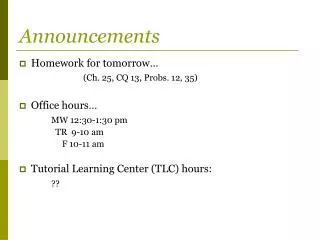

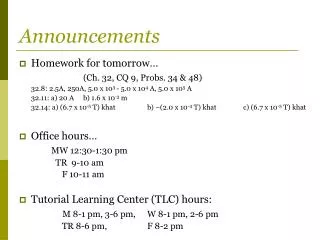

Announcements. mid-term on Thursday 12:30 – be on time . Calculators allowed (required!) No assignment due this week Assignment 6 posted on Thursday Project ideas to me by Nov 1st. Lecture 15 Overview. Digitization Logic families Logic and Gates.

Announcements

E N D

Presentation Transcript

Announcements mid-term on Thursday 12:30 – be on time. Calculators allowed (required!) No assignment due this week Assignment 6 posted on Thursday Project ideas to me by Nov 1st

Lecture 15 Overview • Digitization • Logic families • Logic and Gates

A jump ahead - Lab Information: The Data Flipflop A signal on the D INPUT is transferred to the Q OUTPUT during the positive going transition of the clock pulse. CLEAR and PRESET are independent of the clock and accomplished by a low on the appropriate input. http://fac-web.spsu.edu/cs/faculty/bbrown/web_lectures/sequential/

Digitization • How do we convert a time varying signal into digital bits? • Sampling rate and resolution.

499 PMTs • Photonis XP2970 • 0.15º spacing Camera 1.8 m

Integrated Pulse Data Acquisition • PMT signals digitised with 500MHz sampling FADCs • Data rates • 24 samples/channel • 13.5 kb/event @ 100 Hz • 5 Gb/hour

Cosmic Ray showers measured by VERITAS (each frame 2 ns long)

Logic Gates How do you process a digital signal?

2.4V 0.4V Logic Families: TTL • TTL = transistor-transistor logic • TTL output: LOW<0.4V, HIGH>2.4V • TTL input: LOW < 0.8V, HIGH > 2.0V • Based on BJTs • Supply voltage = 5V

CMOS • CMOS logic = Complementary MOS • Based on MOSFETs • CMOS levels depend upon the supply voltage and provide larger noise margins than TTL • Many other logic families and subtle variations exist - NIM, ECL, LVDS etc. • Generally simple to connect devices from the same logic families together - interfacing different families is more complex (See Horowitz and Hill Ch 9.01)

How do you process a digital signal? • Have only two states • 1,0 map naturally to logic states True/False • Use Boolean algebra • Carry out calculations using a "truth table": list all possible combinations of inputs and corresponding output e.g. • A, B and C are digital signals • n inputs give 2n combinations Each logic function can be performed with logic gate circuit. Digital logic designers do not need to care about what is inside a gate Today's microprocessors can contain >100 million logic gates

The AND gate • The output of an AND gate is TRUE if, and only if, both inputs are TRUE • The symbol for an AND operation is the multiplication symbol "∙" • This is often omitted, so "AANDB" is written "AB" • Note that the truth table looks correct for the multiplication of A and B

The NOT gate • Also known as an inverter • Symbol is the overbar ¯. An apostrophe ' is also used (e.g. A') • There are several realizations of a NOT gate possible • This is the usual schematic symbol • Sometimes it is shown explicitly as a gate • Tying the inputs of a NAND gate together yields a NOT • Tying the inputs of a NOR gate also yields a NOT

The NAND gate • Note the connection between NAND and AND. The output of a NAND gate is the opposite of AND (NAND=NOT AND). • Note the symbol for the NAND operation (AND, NOTed). Schematically, the small circle at the output end of the AND symbol means NOT • NAND is one of the most heavily used binary operations

The OR gate • The output is TRUE if any of the inputs are TRUE • Symbol is +

The NOR gate • The output is TRUE only if all of the inputs are FALSE • Inverse of OR

Gate Combination Which of the following inputs gives D=1 ? • Answer: a and c

Gate Combinations • What is the truth table for this circuit? • The effect of this circuit is the same as an XOR gate.

The XOR gate C=AXORB C=AB C • Exclusive OR • The output is TRUE only if one or the other, but not both, inputs are TRUE • Symbol is • The XOR gate can be used as an "optional inverter" • e.g. to invert or not invert an input signal at B, based on a controlling input at A

The XNOR gate C=ANORB C=AB C • Inverse of XOR • The output is TRUE only if both inputs are the same. • "logical equality"