Test Data Generation for LRU Cache Memory Testing

Develop test programs for evaluating LRU cache memory by simulating test scenarios and dependencies, ensuring comprehensive microprocessor coverage. The model ensures data integrity and efficient cache management.

Test Data Generation for LRU Cache Memory Testing

E N D

Presentation Transcript

Test Data Generation for LRU Cache-Memory Testing Evgeny KornikhinMoscow State UniversityInstitute for System Programming of RAS

testing by test programs add r1,r2,r3sub r4, r1, r2lw r5, r1, 0lui r2, r1, r4 Y/N assembly program ( test program ) microprocessor

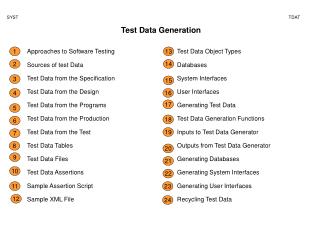

test program generation model of microprocessor coverage oftest situations and dependencies (r-w, r-r) add r1,r2,r3 @ overflow lw r4, r3, c @ hit test templates (logical form) mov r2, 0xFF add r1,r2,r3 lw r4, r3, 0 test programs (executable form)

R4000 add load ... args test situations cache rd rs rt overflow regular test program generation model of microprocessor coverage oftest situations and dependencies (r-w, r-r) add r1,r2,r3 @ overflow lw r4, r3, c @ hit test templates (logical form) mov r2, 0xFF add r1,r2,r3 lw r4, r3, 0 test programs (executable form)

R4000 add load ... args test situations cache rd rs rt overflow regular test program generation model of microprocessor coverage oftest situations and dependencies (r-w, r-r) add r1,r2,r3 @ overflow lw r4, r3, c @ hit test templates (logical form) mov r2, 0xFF add r1,r2,r3 lw r4, r3, 0 test programs add specific initialization of microprocessor (registers and cache) (executable form)

cache-hit cache model tag0' value0' tag0'' value0'' set №0 LOAD val, addr (val := memory[addr]) t' v' t'' v'' set №s

cache-hit cache model tag0' value0' tag0'' value0'' set №0 LOAD val, addr (val := memory[addr]) addr t = t' ort = t'' t s t = t'' tag set t' v' t'' v'' set №s

cache-miss cache model tag0' value0' tag0'' value0'' set №0 LOAD val, addr (val := memory[addr]) nextlevel addr t != t' andt != t'' t s tag set t' v' t'' v'' set №s evicted

LOAD x, y @ hitSTORE u, z @ missLOAD z, y @ hit problem again initial state of cacheand registers = ?

key idea test template add ...load …sub …div … LOAD x, y @ hit constraint variable ? ? ? ? y {a,b,c} ? ? variable u {a,b,c} cache model x = z

fully associative cache z x z x y ... N y {x,y,z,...} - current state

cache-hit hit(t) z t x z x y ... N y t {x,y,z...}

cache-miss miss(t) z t x z x y ... N y t {x,y,z...} newcache={x,y,z...}{t}\{?}

cache-miss miss(t)→u z t x z x y ... N y t {x,y,z...} u{x,y,z...} newcache={x,y,z...}{t}\{u}

lru(u) hit x1 u = x2 hit x2 {x3, x5} = L\{u} miss x3->x4 hit x5 L miss t->u counter(u)=min

lru(u) hit x1 u = x1 hit x2 {x2, x3, x5} = L\{u} miss x3->x4 hit x5 L miss t->u there are another cases

example a initialstate: b y{a,b,g} g z{a,b,g} LOAD x, y @ hit z0{a,b,g} →z0 STORE u, z @ miss z0=b {a,b,g}\{z0}={g,y} LOAD z, y @ hit y{a,b,g,z}\{z0} N = 3

example z{a,b,g} y = a y{a,b,g} z{a,b,g} y=a=0 z0{a,b,g} z0=b {a,b,g}\{z0}={g,y} b=1 g=2 z=3 y{a,b,g,z}\{z0}

common cache x x R(x) y R(y) y z z R(z)

common cache hit(t) t L miss(t)→u u Lt L new cache=L{t}\{u}R(t) = R(u)lru(u)

lru(u) hit x1 hit x2 u = x2 {x3, x5}∩R(u) = (L\{u})∩R(u) miss x3→x4 hit x5 miss t→u

example x1,x2 {a1,a2,b1,b2,c1,c2} x3 {a1,a2,b1,b2,c1,c2} R(x3) = R(y3) x4 {a1,...,c2,x3}\{y3} x5 {a1,...,c2,x3}\{y3} y3 = c2 {y3} = ({a1,...,c2}\{x1,x2, y3})∩R(y3) y5 = x2 {y5} = ({a1...c2,x3}\{y3,y5, x3,x4})∩R(y5)

SAT modulo theories (bit-vectors) Yices solver (assert (or (= x a) (= x b)(= x c))) x {a,b,c} y {a,b,c} (assert (and (/= y a) (/= y b)(/= y c))) x = z (check) SMT

http://tesla-project.googlecode.com http://hardware.ispras.ru kornevgen@gmail.com contacts