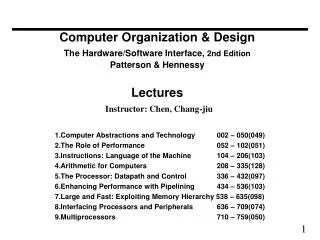

Cosc 235: Computer Organization

Cosc 235: Computer Organization. Boolean Algebra and Logic Gates. The Boolean Equation. The outcome of passing digital levels through a network of switches can be predicted with an algebraic equation. George Boole formed this algebra in 1854

Cosc 235: Computer Organization

E N D

Presentation Transcript

Cosc 235: Computer Organization Boolean Algebra and Logic Gates

The Boolean Equation • The outcome of passing digital levels through a network of switches can be predicted with an algebraic equation. • George Boole formed this algebra in 1854 • Boolean algebra was aimed at true-false logic and theorem proving • Assumption that any proposition can be proven with correct answers to a specific number of true-false questions

The Boolean Equation • The Boolean operation may point out the redundancy of variables • Since Boolean algebra deals with the dual states, it lends itself readily to binary machines • In this application, it can be used to determine the correctness of a circuit • Useful for determining redundancies in circuits

A B AB 0 0 0 0 1 0 1 0 0 1 1 1 A B A+B 0 0 0 0 1 1 1 0 1 1 1 1 Boolean Algebra • Operators: • AND ( like multiply) • OR (like add) • NOT (negation) A ~A or A 0 1 1 0

Boolean Algebra • Commutative Law • A + B = B + A • AB = BA • Associative Law • A + (B + C) = (A + B) + C • A(BC) = (AB)C • Distributive Law • A(B + C) = AB + AC

Boolean tautologies • AND with 0: 0 0 = 0 | 0 1 = 0 | 0 A = 0 • OR with 1: 0 + 1 = 1| 1 + 1 = 1| 1 + A = 1 • AND with 1: 1 1 = 1 | 1 A = A • OR with 0: 0 + 0 = 0| 0 + A = A • Variables with themselves: • A A = A A ~A = 0 • A + A = A A + ~A = 1 • ~(~A) = A

Logic Gate Symbols • AND • OR • NOT Generate these gates with transistor circuitry

Logic Gate Symbols • The logic symbols for AND, OR, NOT appear on logic drawings which are used to design and document switching networks • The symbols apply whether the functions are produced with manual switches or with electronic circuits

Example logic gate circuits AB AB+C = AB+C A+B (A+B)C = AC + BC How else could we wire this?

Example logic gate circuits • X = D + ABC • X = CD(A+B) • X = ACD + AEF + BCD + BEF

Equivalent logic circuits AC+BC+AD+BD = C(A+B) + D(A+B) = (A+B)(C+D) AC BC AD BD

NAND • An AND gate with output inverted is called a NAND gate X = AB

NOR • An OR gate with output inverted is called a NOR gate X = A+B

Example logic gate circuits • X = AB + CD • X = (A + B)(C + D) • X = (A + B) + (C + D)

Factoring Inverted Terms • Terms can be factored under inversion bars • X = AC + AB = A(C+B) • We cannot separate the inversion bars • A + B A + B • A B A B

A + B + C = A B C A B C = A + B + C DeMorgan’s Theorem • The compliment of an OR function is equal to the AND function of the compliments • The compliment of an AND function is equal to the OR function of the compliments

DeMorgan’s Theorem • Therefore, we have 2 valid symbols for NOR: • DeMorgan’s Theorem is often useful in simplifying circuit functions

Simplifying Boolean equations • “X is true iff ABC or ABC or ABC or ABC” A B AB+AB+AB 0 0 0 0 1 1 1 0 1 1 1 1 1. Consider part in ( ) using a truth table: A+B! So f = C(A+B)+AB

Simplifying Boolean equations • “X is true iff ABC or ABC or ABC or ABC” 2. Consider part in ( ) using Boolean Algebra: A+B! So f = C(A+B)+AB

AB AB AB AB C C Karnough Mapping • Used for gate minimization • The map of a general logic function of 3 variables looks like: • Each square in the map corresponds to one of the 8 possible combos of the variables • Adjacent squares differ by only one variable

AB AB AB AB C 1 1 C 1 Karnough Mapping Example • Minterm form of the equation: disjunction of simple conjunctions

AB AB AB AB C C Karnough Mapping Example • What does it mean that adjacent squares differ by the value of only one variable? • Examine a 2-square group • Note lack of dependence on one of the 3 variables • Watch for wraparound AC AB BC C BC

AB AB AB AB C 1 C 1 Karnough Mapping Examples • Boolean algebra also shows this • Consider also:

Karnough Mapping • 4 square groups are also possible • 4-square groups indicate that there is no dependence on 2 of the variables (22=4)

Mapping in 4 variables AB AB AB AB CD CD CD CD ABC D

Example in 4 variables AB AB AB AB CD 1 1 1 1 CD 1 CD CD 1 1

Negative Karnough Mapping • Look where 0’s exist in the K-map • Generate that function • Invert the results

Don’t Care conditions • There may be a situation where entries in the truth table are not specified • Choose the “Don’t Care” positions to get the simplest possible logic circuit A B C X 0 0 0 0 0 0 1 x 0 1 0 1 0 1 1 x 1 0 0 0 1 0 1 0 1 1 0 x 1 1 1 1

Jogger decision circuit • Suppose a jogger has the following problem: • The only time available to jog is early in the morning. • Jogger is not a morning person, i.e., does not think well for a significant period of time after rising--especially early in the morning. • Deciding whether to jog and what clothes to wear if jogging is a difficult problem

Jogger decision circuit • Design a combinational logic system which will make these decisions • Input: weather and jogger’s sensitivity to it • these input values must be sensed & converted to digital signals • transducers • W: wind (0: <10 mph; 1: >= 10 mph) • P: precipitation (0: no precip; 1: precip) • TE: temperature (00: temp <-20C; 01: -20C <= temp < 0C 11: 0C <= temp < 15C 10: 15 <= temp)

O1O0=00 if TE O1O0=01 if PTE + WTE O1O0=10 if TE Jogger decision circuit • Output: Jogging decision 00: go back to bed • if temp < -20C 01: Jog, wear maximum clothing • if precip & -20C <= temp < 0C or • if wind >= 10mph & -20C <= temp < 0C 11: Jog, wear jogging suit • if precip & 0C <= temp < 15C 10: Jog, wear shorts and T-shirt • if 15C <= TE • Use a these as input to a decoder that tells the jogger what to do O1O0=11 if PTE

O1O0 O1O0=00 if TE 00 00 00 00 xx xx xx 01 01 01 O1O0=01 if PTE + WTE 11 11 10 10 10 10 O1O0=10 if TE Jogger decision circuit O1O0=11 if PTE

O1O0 00 00 00 00 xx xx xx 01 01 01 11 11 10 10 10 10 O0 O1 0 0 0 0 0 0 0 0 x 1 1 1 X 1 1 x x 0 0 0 x 1 1 x 0 0 0 0 1 1 1 1 Jogger decision circuit

O1 0 0 0 0 x 0 0 0 x 1 1 x 1 1 1 1 Jogger decision circuit • Choose “don’t care” x’s to minimize gates TEWP = TEWP = 1 TEWP = 0 O1 = T

O0 0 0 0 0 x 1 1 1 X 1 1 x 0 0 0 0 Jogger decision circuit • Choose “don’t care” x’s to minimize gates • O0 = E

Functionally Complete Gates • A set of gates S is functionally complete if every function can be computed using only gates from S. • {AND, OR, NOT} • {AND, NOT} • {OR, NOT} • {NAND}

Exclusive OR A B AB 0 0 0 0 1 1 1 0 1 1 1 0

Useful things to do with Exclusive OR • Complimenting Gate • Control line LO: OUT=IN • Control line HI: OUT=IN • Parity generator • XOR each bit with the previous result • Parity tree • Comparitor • XOR each bit from 2 numbers • OR results: if 1, not same; if 0, same

Decoder • Take an n-bit number as input • Select exactly one of the 2n output lines, set its output to 1 (others 0) • Can be used, e.g., to select one of a number of memory modules to be active • Circuit design process

Decimal decoders • BCD Decoder 0=0000 1=0001 2=0010 3=0011 4=0100 5=0101 6=0110 7=0111 8=1000 9=1001 x=1010 x=1011 x=1100 x=1101 x=1110 x=1111 Raise a line corresponding to the input. • 1 big decoder or multiple small decoders?

a f b g e c d Decimal decoders • Application: 7-segment display 0: a, b, c, d, e, f 4: b, c, f, g 8: a, b, c, d, e, f, g 1: b, c 5: a, c, d, f, g 9: a, b, c, f, g 2: a, b, d, e, g 6: a, c, d, e, f, g 3: a, b, c, d, e 7: a, b, c

Encoders • Opposite function from a decoder • Generates specific codes according to a suite of input lines • Encode which line has been raised • E.g., keypad entry

Multiplexer • Circuit with 2n inputs, one output, n control lines • Control lines select which input to connect to the output • Circuit design process

Demultiplexer • Circuit with 1 input, 2n outputs, n control lines • Control lines select which output line to connect to the input • Circuit design

Adders A = 111 +B = 101 1100 How do we add? Look at LSB first A0 B0 S0 C1 0 0 0 0 0 1 1 0 1 0 1 0 1 1 0 1 XOR AND Circuitry to implement this is called a “Half Adder”