Multiplexers

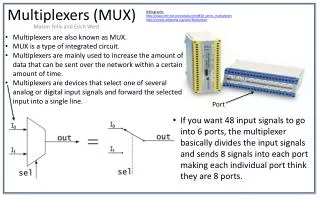

Multiplexers. Lecture L6.6 Section 6.2. Multiplexers. A Digital Switch A 2-to-1 MUX A 4-to-1 MUX A Quad 2-to-1 MUX The ABEL when…then Statement TTL Multiplexer. 4 x 1. MUX. s1. s0. Y. 0 0 C0 0 1 C1 1 0 C2 1 1 C3. Multiplexers. C0. C1. Y. C2. C3. s1. s0.

Multiplexers

E N D

Presentation Transcript

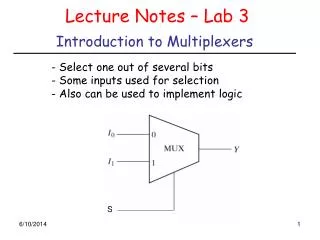

Multiplexers Lecture L6.6 Section 6.2

Multiplexers • A Digital Switch • A 2-to-1 MUX • A 4-to-1 MUX • A Quad 2-to-1 MUX • The ABEL when…then Statement • TTL Multiplexer

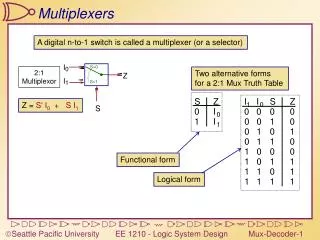

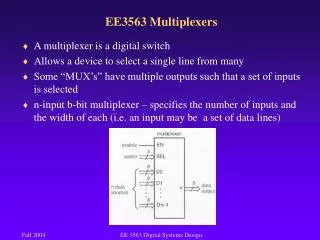

4 x 1 MUX s1 s0 Y 0 0 C0 0 1 C1 1 0 C2 1 1 C3 Multiplexers C0 C1 Y C2 C3 s1 s0

4 x 1 MUX Multiplexers s1 s0 Y C0 0 0 C0 0 1 C1 1 0 C2 1 1 C3 C1 Y C2 C3 s1 s0 A multiplexer is a digital switch 0 0

4 x 1 MUX Multiplexers s1 s0 Y C0 0 0 C0 0 1 C1 1 0 C2 1 1 C3 C1 Y C2 C3 s1 s0 0 1

4 x 1 MUX Multiplexers s1 s0 Y C0 0 0 C0 0 1 C1 1 0 C2 1 1 C3 C1 Y C2 C3 s1 s0 1 0

4 x 1 MUX Multiplexers s1 s0 Y C0 0 0 C0 0 1 C1 1 0 C2 1 1 C3 C1 Y C2 C3 s1 s0 1 1

A 2 x 1 MUX Z = A & !s0 # B & s0

A 4 x 1 MUX A = !s0 & C0 # s0 & C1 B = !s0 & C2 # s0 & C3 Z = !s1 & A # s1 & B Z = !s1 & (!s0 & C0 # s0 & C1) # s1 & (!s0 & C2 # s0 & C3)

A 4 x 1 MUX Z = !s1 & (!s0 & C0 # s0 & C1) # s1 & (!s0 & C2 # s0 & C3) Z = !s1 & !s0 & C0 # !s1 & s0 & C1 # s1 & !s0 & C2 # s1 & s0 & C3

S Y 0 A 1 B ProblemHow would you make aQuad 2-to-1 MUX? Quad 2-to-1 MUX [A3..A0] [Y3..Y0] [B3..B0] S

mux.abl MODULE Mux TITLE 'Quad 2 to 1 Multiplexer, A. Student, 6/21/02' DECLARATIONS " INPUT PINS “ " OUTPUT PINS “ EQUATIONS END Mux Quad 2-to-1 MUX [A3..0] [Y3..0] [B3..0] S

Switch S6(1..4) A input vector (4 bits) Switch S7(1..4) B input vector (4 bits) Push Button Select Line mux.abl MODULE Mux TITLE 'Quad 2 to 1 Multiplexer' DECLARATIONS " INPUT PINS " A3..A0 PIN 11,7,6,5; A = [A3..A0]; B3..B0 PIN 4,3,2,1; B = [B3..B0]; S PIN 10;

Defines output Output LEDs 9 – 12 Output Vector Y (4 bits) Logic Equation for the Multiplexer mux.abl (cont’d) " OUTPUT PINS " Y3..Y0 PIN 35,36,37,39 ISTYPE 'com'; Y = [Y3..Y0]; EQUATIONS Y = A & !S # B & S; END Mux

Mux Using Behavioral ABEL Z = !s2 & !s1 & !s0 & C0 # !s2 & !s1 & s0 & C1 # !s2 & s1 & !s0 & C2 # !s2 & s1 & s0 & C3 # s2 & !s1 & !s0 & C4 # s2 & !s1 & s0 & C5 # s2 & s1 & !s0 & C6 # s2 & s1 & s0 & C7

MODULE mux81 TITLE '8 to 1 Multiplexer' DECLARATIONS " INPUT PINS " C7..C0 PIN 11,7,6,5,4,3,2,1; C = [C7..C0]; s2..s0 PIN 70,71,72; S = [s2..s0]; " OUTPUT PINS " Z PIN 35 ISTYPE 'com'; EQUATIONS when (S == 0) then Z = C0; when (S == 1) then Z = C1; when (S == 2) then Z = C2; when (S == 3) then Z = C3; when (S == 4) then Z = C4; when (S == 5) then Z = C5; when (S == 6) then Z = C6; when (S == 7) then Z = C7; @radix 16; test_vectors ([C,S] -> Z) [6,0] -> 0; [7,1] -> 1; [9,2] -> 0; [15,3] -> 0; [36,4] -> 1; [47,5] -> 0; [29,6] -> 0; [0A5,7] -> 1; END mux81.abl

MODULE mux81 TITLE '8 to 1 Multiplexer' DECLARATIONS " INPUT PINS " C7..C0 PIN 11,7,6,5,4,3,2,1; C = [C7..C0]; s2..s0 PIN 70,71,72; S = [s2..s0]; " OUTPUT PINS " Z PIN 35 ISTYPE 'com';

EQUATIONS when (S == 0) then Z = C0; when (S == 1) then Z = C1; when (S == 2) then Z = C2; when (S == 3) then Z = C3; when (S == 4) then Z = C4; when (S == 5) then Z = C5; when (S == 6) then Z = C6; when (S == 7) then Z = C7;

@radix 16; test_vectors ([C,S] -> Z) [6,0] -> 0; [7,1] -> 1; [9,2] -> 0; [15,3] -> 0; [36,4] -> 1; [47,5] -> 0; [29,6] -> 0; [0A5,7] -> 1; END

Blif Simulation Report 8 to 1 Multiplexer C C C C C C C C s s s 7 6 5 4 3 2 1 0 2 1 0 Z V0001 0 0 0 0 0 1 1 0 0 0 0 L V0002 0 0 0 0 0 1 1 1 0 0 1 H V0003 0 0 0 0 1 0 0 1 0 1 0 L V0004 0 0 0 1 0 1 0 1 0 1 1 L V0005 0 0 1 1 0 1 1 0 1 0 0 H V0006 0 1 0 0 0 1 1 1 1 0 1 L V0007 0 0 1 0 1 0 0 1 1 1 0 L V0008 1 0 1 0 0 1 0 1 1 1 1 H 8 out of 8 vectors passed.

1 16 1G Vcc 2 15 B 2G 3 14 1C3 A 4 13 1C2 2C3 5 12 1C1 2C2 6 11 1C0 2C1 7 10 1Y 2C0 8 9 GND 2Y 74LS153 TTL Multiplexer B A C0 C1 C2 C3 G Y X X X X X X 1 0 0 0 0 X X X 0 0 0 0 1 X X X 0 1 0 1 X 0 X X 0 0 0 1 X 1 X X 0 1 1 0 X X 0 X 0 0 1 0 X X 1 X 0 1 1 1 X X X 0 0 0 1 1 X X X 1 0 1 Dual 4-to-1-line multiplexer