CPU DESIGN PROJECT

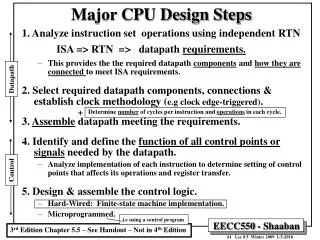

This project focuses on the design of a CPU that utilizes a multicycle datapath, featuring 16 registers and an Instruction Set Architecture (ISA) consisting of 16 instructions with 4-bit opcodes. The design includes R-type, I-type, J-type, and B-type instructions, along with a detailed control unit and various processing elements. Challenges encountered include limited offset values and the implementation of a hardwired control unit. Future improvements may involve a microprogrammed control unit and optimizations for faster execution and reduced critical path delays.

CPU DESIGN PROJECT

E N D

Presentation Transcript

CPU DESIGN PROJECT ADITI SHINDE CHIDAMBARAM ALAGAPPAN

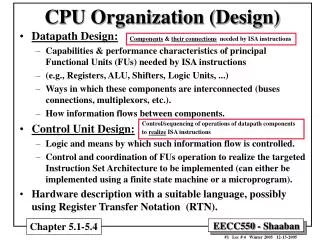

Features • MulticycleDatapath • 16 Registers • 16 instructions having 4 bit opcode

ISA • R -TYPE: • I TYPE • J-TYPE • B-TYPE

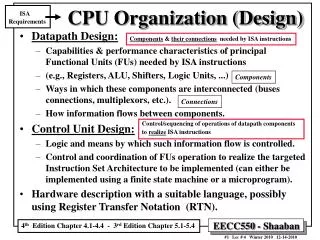

MulticycleDatapath PCS PCW 12 to 15 to Control FSM 0-11 RW 8-11 4-7 Instr. reg. (IR) A PC Addr. 0-3 Memory ALU Register file ALUA ALUB AOut ID Data Mem. Data Reg(MDR) B RD IRW 1 Sign extend Control unit MRg -1 MW 12-15

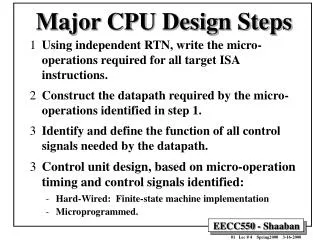

Instr. decode/reg. fetch/branch addr. Instr. fetch/ adv. PC ALU operation Write PC on branch condition Write jump addr. to PC Compute memory addr. Write memory data Read memory data Write register Write register FSM Start State 0 1 lw or sw J R B 3 2 lw 6 8 9 sw 4 5 7

INSTRUCTION SET 1. Add 2. Sub 3. And 4. Or 5. Nor 6. Slt 7. Lw 8. Sw 9. Addi 10. Andi 11. Beq 12. Jump 13. Jal 14. Jr

PROBLEMS FACED • Smaller value of offset (4 bits) • Halt – Hardwired -1

PROSPECTIVE CHANGES • Micro programmed Control Unit • Hardware changes for faster execution • Effective programming for preventing latches • Reduce critical path delay for accommodating faster execution