Memory Access Scheduling

Memory Access Scheduling. Taidi Chen Fall 2006. Background. Memory bandwidth bottleneck 3-D structure of banks, rows and columns characteristic of DRAM chips bank precharge row activation column access

Memory Access Scheduling

E N D

Presentation Transcript

Memory Access Scheduling Taidi Chen Fall 2006

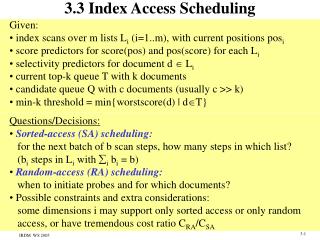

Background • Memory bandwidth bottleneck • 3-D structure of banks, rows and columns characteristic of DRAM chips • bank precharge row activation column access • Memory access scheduling reorder memory operations to exploit the non-uniform access time of the DRAM

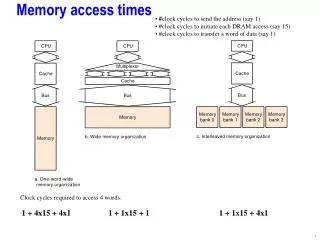

DRAM architecture • 3-D architecture of DRAM • Timing and resource constraint • bank state diagram • Resource utilization • Shared address

Bank state diagram • Idle state • Precharge and ready for a row access • Switch to active state when a row activate operation is issued • Active state • the content of the selected row are held in the bank’s row buffer • Column access • Switch to idle state when a precharge operation is issued

Resource Utilization • Both precharge and row operation occupied the bank resource • Data return from read after three cycles • Data to write must be transfer to DRAM at the time of issue

Scheduling policies (I) • In-order • Operation will only be performed if it is required by the oldest pending reference • Priority • Operation required by the highest priority ready references are performed • Ordered – older references are given higher priority • Age-threshold – references older than some threshold age gain increased priority • Load-over-store – load references are given higher priority

Scheduling policies (II) • Open • A bank is only precharged if there are pending reference to other rows in the bank and there are no pending reference to the active row • Take advantage of row locality • Closed • A bank is precharged as soon as there are no more pending references to the active row

Scheduling policies (III) • Most pending • The row or column access to the row with the most pending references is selected • Active row has highest column to row access ratio • Fewest pending • Selects the column access to the row targeted by the fewest pending references • Minimize the time that rows with little demand remain active

Conservative Scheduling • Also known as First-ready scheduling • Use the ordered priority scheme • Allow access to different banks at the same time • Improve up to 79%

Aggressive scheduling • Take advantage of open/closed policies • Improve up to 106-144%

Aggressive scheduling (106-144%) (27-30%) (85-93%)

Intel P965 chipset Source: Intel.com

Intel P965 chipset source: Intel.com