A Modern CMOS Process

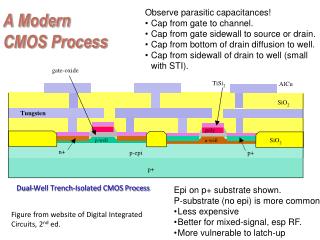

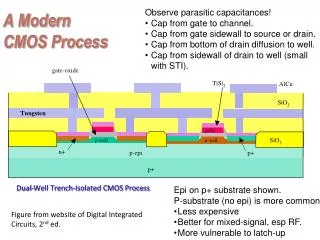

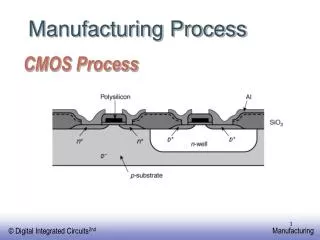

A Modern CMOS Process. Observe parasitic capacitances! Cap from gate to channel. Cap from gate sidewall to source or drain. Cap from bottom of drain diffusion to well. Cap from sidewall of drain to well (small with STI). Dual-Well Trench-Isolated CMOS Process. Epi on p+ substrate shown.

A Modern CMOS Process

E N D

Presentation Transcript

A Modern CMOS Process • Observe parasitic capacitances! • Cap from gate to channel. • Cap from gate sidewall to source or drain. • Cap from bottom of drain diffusion to well. • Cap from sidewall of drain to well (small with STI). Dual-Well Trench-Isolated CMOS Process • Epi on p+ substrate shown. • P-substrate (no epi) is more common • Less expensive • Better for mixed-signal, esp RF. • More vulnerable to latch-up Figure from website of Digital Integrated Circuits, 2nd ed.

Gate Capacitance Cut-off Resistive Saturation Most important regions in digital design: saturation and cut-off To each Cgs entry in the table, add Cgso; to each Cgd entry, add Cgdo. Cgdo = CGDO∙W, Cgso = CGSO∙W

Diffusion Capacitance Channel-stop implant Side wall Source W N D Bottom x Side wall j Channel L Substrate N S A Drawing assumes LOCOS isolation. Obsolete, but consistent with many examples in text. Formula is ok.

Interconnect: Wires connecting transistors http://www.avii-ic.com/Figure5r.gif Interconnect has parasitic resistance and capacitance