COMBINATIONAL LOGIC

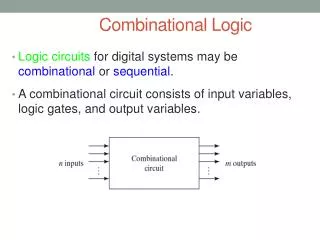

COMBINATIONAL LOGIC. Overview. Combinational vs. Sequential Logic. At every point in time (except during the switching. transients) each gate output is connected to either. V. or. V. via a low-resistive path. DD. ss. The outputs of the gates assume at all times the value.

COMBINATIONAL LOGIC

E N D

Presentation Transcript

At every point in time (except during the switching transients) each gate output is connected to either V or V via a low-resistive path. DD ss The outputs of the gates assumeat all timesthevalue of the Boolean function, implemented by the circuit (ignoring, once again, the transient effects during switching periods). This is in contrast to the dynamic circuit class, which relies on temporary storage of signal values on the capacitance of high impedance circuit nodes. Static CMOS Circuit

NMOS Transistors in Series/Parallel Connection • Transistors can be thought as a switch controlled by its gate signal • NMOS switch closes when switch control input is high A B NAND Gnd = Y = X if A and B X Y A NOR B Gnd = Y = X if A OR B X Y NMOS Transistors pass a “strong” 0 but a “weak” 1

PMOS Transistors in Series/Parallel Connection Vdd = NOR NAND Vdd =

Example Gate: COMPLEX CMOS GATE F = D(A+BC) F = D +A(B+C)

4-input NAND Gate Vdd Out GND In1 In2 In3 In4

DC Characteristics of 2-Input NAND VOH = Vdd VOL = Gnd • VLT: Different based on Input • 11 – 01 • 11 – 10 • 11 -- 00 Va 11 – 01: Similar to Inverter with resistor in source circuit 11 – 10: Similar to Inverter with resistor in drain circuit 11 – 00: Similar to Inverter with b’p = 2bp & b’n = 1/2bn Vb

DC Characteristics of 2-Input NAND Vgs1 = VLT; Vgs2 = VLT – Vds1; VLT = Vds1 + Vds2 Vgs2 = Vds2 M2 is saturated M1 is linear Id; VLT M2 VLT M1 Parallel Combination:

DC Characteristics of 2-Input NAND • In design: • Set one (middle) VLT = Vdd/2 • Distribute about Vdd/2 • Make mean = Vdd/2

Pseudo-NMOS NAND Gate VDD GND

Improved Loads • M2 is long (large resistance) • M1 is enabled when A, B, C and D have been asserted. • Fast Pull-Up • Low VOL • More power consumption

Improved Loads (2) V V DD DD • Only useful if Out & Out are needed. M1 M2 Out Out A A PDN1(F) PDN2 (not F) B B V V SS SS Complementary Dual (differential) Cascode Voltage Switch Logic (DCVSL)

Pass-Transistor Logic B Out A Switch s t Out u p n Network B I B • N transistors (small) • No static consumption

C = 5 V Vg= 5 V M 2 A = 5 V B Vd = 5 V M n Vs M C 1 L does not pull up to 5V, but 5V - V B Threshold voltage loss causes static power consumption NMOS-only switch (Passing a “1”) [Vtn(Vsb) > |Vtp|] M2 is ON V TN

C = 5 V Vg= 5 V M 2 A = 5 V B Vs = 0 V M n Vd M C 1 L does pull up to 0V V B No threshold voltage loss causes No static power consumption NMOS-only switch (Passing a “0”)

C = 5 V Vg= 5 V M 2 A = 5 V B Vs = 0 V M n Vd M C 1 L NMOS-only switch (Transient Response)

Transmission Gate • Parallel combination of NMOS and PMOS • Full signal swing since: • NFET “0” well • PFET “1” well • Improved speed (parallel resistors) • Larger & requires inverter

30000.0 (W/L) =(W/L) = p n 1.8/1.2 20000.0 ) m h O ( R 10000.0 0.0 0.0 1.0 2.0 3.0 4.0 5.0 Vout Resistance of Transmission Gate R n For Tgate passing a “1” R p R eq

S S Pass-Transistor Based Multiplexer S VDD GND In1 In2 S

Delay Optimization Mopt ~ 3 - 4