Viterbi Decoder Project

This appendix outlines the operational procedures for the Viterbi Decoder project cage, generously provided by Qualcomm Israel. It details the development of a module that showcases the harmonious functioning of the FPGA and DSP. Readers will learn about essential bus rates, the DSP's operation at 160 MHz, and the critical role of the arbiter at 40 MHz. The document also includes instructions for code uploading, connecting to the cage via CRT or Telnet, and accessing memory through PES, enhancing the understanding of this advanced technology.

Viterbi Decoder Project

E N D

Presentation Transcript

Viterbi Decoder Project Alon weinberg, Dan Elran Supervisors: Emilia Burlak, Sara Galan

Appendix- cage operation This is the appendix to the Viterbi Decoder project, in which we learn how to operate the cage (donated by Qualcomm Israel) and write a small module that demonstrates the cage operation- shows how the FPGA works, how the DSP works and how they both work together in harmony.

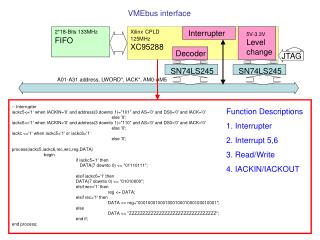

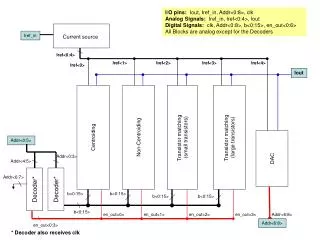

Board bus rates • DSP works at 160 MHz • BUT Arbiter works at 40 MHz (Bottleneck) • Periferial BUS (PCI) • Local Bus • PLX and DSP can master both buses • Asynched I/O RAMs connected to FPGAs

PES PES is the software running on the VXWorks RT OS on the cage, written by Qualcomm Israel. It is the Cage Driver, and has service functions like reading and writing memory addresses on the FPGA/DSP.

Code Uploading • Hex files • FTP to cage • /FIRMWARE/FMC/ for FPGA code (same for both FPGAs) • /DSP/FMC/ for DSP code • Reboot

Connecting • CRT (or similar?) • Telnet (IP address) or serial cable (if serial- 9600 Baud rate, no flow control)

Memory access (PES) • Mww(slot number, address, value) • Mrw (slot number, address) • Add 2 to the PES slot number • Base addresses- in HSID

Memory access (DSP C code) • CONTENTS_OF( address) • Base addresses- in the C header files