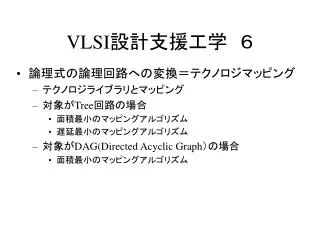

VLSI 設計支援工学 6

VLSI 設計支援工学 6. 論理式の論理回路への変換=テクノロジマッピング テクノロジライブラリとマッピング 対象が Tree 回路の場合 面積最小のマッピングアルゴリズム 遅延最小のマッピングアルゴリズム 対象が DAG(Directed Acyclic Graph )の場合 面積最小のマッピングアルゴリズム. テクノロジライブラリをマッピング. 論理式簡単化結果 積和形論理式と中間変数の集まり LSI で用意されている基本回路(セル) NAND, NOR, AND, OR AOI(And Or Inverter), OAI(Or And Inverter)

VLSI 設計支援工学 6

E N D

Presentation Transcript

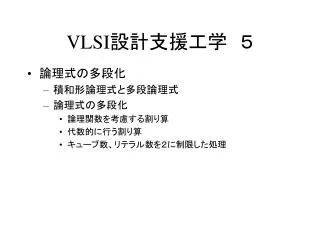

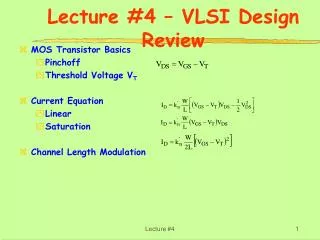

VLSI設計支援工学 6 • 論理式の論理回路への変換=テクノロジマッピング • テクノロジライブラリとマッピング • 対象がTree回路の場合 • 面積最小のマッピングアルゴリズム • 遅延最小のマッピングアルゴリズム • 対象がDAG(Directed Acyclic Graph)の場合 • 面積最小のマッピングアルゴリズム

テクノロジライブラリをマッピング • 論理式簡単化結果 • 積和形論理式と中間変数の集まり • LSIで用意されている基本回路(セル) • NAND, NOR, AND, OR • AOI(And Or Inverter), OAI(Or And Inverter) • XOR, XNOR • トランジスタの大きさが異なるセル • ドライブ能力が違う • コスト • 面積最小、遅延最小、消費電力最小

f t1 g d out t2 e h t3 t5 b t1 = fgh t2 = d + e t3 = b + h t4 = at3 + c out = t1t5 a t4 c

not(1) nand2(2) nand3 (3) and2(3) or(3) oai21 (3) aoi22 (4)

f g d out e h b a 面積合計23 c

and2(3) f g aoi22(4) or2(3) d out e h or2(3) nand2(2) b a nand2(2) c 面積合計18 not(1)

f nand3(3) g and2(3) oai21(3) d F e h b oai21 (3) a 面積合計15 nand2(2) c not(1)

面積最小のマッピング-対象がTree回路の場合-面積最小のマッピング-対象がTree回路の場合- • 動的プログラミング(Dynamic Programming)の典型 • 要点 • 入力から現在のゲートまでの部分回路の最適マッピングは、現在のゲートより出力側のゲートには依存しない • 遅延最小化のマッピングでは成立しない • 第1ステップ • 回路を入力から順に辿り、入力から現在のゲートまでの部分回路に対する最適マッピングのみを保存していく • 第2ステップ • 回路を出力から入力へ辿りながら、最適マッピングを決定していく

nand2 (3) not (2) nand3 (4) nand4 (5) and2 (4) aio21 (4) oai21 (4) library

nand2(3) not(10) aoi21(8) 5 6 7 not(6) and2(8) nand2(12) nand3(11) nand4(8) 8 not(5) and2(4) nand2(3) nand2(11) nand3(13) nand4(12) nand2(7) nand3(4) 4 1 2 3

aoi21 5 6 7 8 nand2 nand3 4 1 2 3 (d) 図6

load=3 遅延最小のマッピング-対象がTree回路の場合- • ゲートの遅延は、その負荷(キャパシタンス)の大きさで変化する: delay = base_delay + αΣ(fanout_capacitance) • アルゴリズムの修正 • 第1ステップ • 負荷容量はn 個の領域値loadi, 1i n に分ける • それぞれに負荷領域 loadiごとに遅延最小セルcelliを決定する • 第2ステップ • 回路の出力から入力へ、実際の負荷容量 loadjを使ってベストなセル celljを選んでいく load ? INV or AND2 ?

1 2 3 4 NAND3 load=3 1 2 NAND3 load=1 3 4 INV load=3 遅延最小化マッピングの例

対象がDAG(Directed Acyclic Graph)の場合-面積最小のマッピングアルゴリズム- • 方法1: Treeに分ける

対象がDAG(Directed Acyclic Graph)の場合-面積最小のマッピングアルゴリズム- • 方法2: DAG用のcovering アルゴリズム • NPハード • 各ノード(ゲート)とライブラリのセルの可能なマッチを全て求め、{mk}とする • 各mkに対し、そのノードをカバーする条件を論理式にする • 例: もしそのノードをカバーできるマッチが、m2, m5, m10の場合には、(m2 + m5 + m10)という条件式を生成する • マッチmiのn 個の入力がノードsi1, …, sinに接続されている場合、miが選ばれた場合には、ノードsi1, …, sinの出力の実現されていなけらばならない • 回路の出力が実現されていなければならない • 各マッチには、使用するセルに対応したコスト(面積)がつく。最小コストで、上記の制限を満たす{mk}の値の組合せを求める

p duces gate cost inputs ro covers m 1 inv b g g 1 1 1 m 1 a inv g g 2 2 2 m nand2 2 g ; g g g 3 1 2 3 3 m nand2 2 a; b g g 4 4 4 m nand2 2 g ; g g g 5 3 4 5 5 m 1 inv g g g 6 4 6 6 m nand2 2 g ; c g g 7 6 7 7 m 1 inv g g g 8 7 8 8 m nand2 2 g ; d g g 9 8 9 9 m nand3 3 g ; c; d g g ; g ; g 10 6 9 7 8 9 m nand3 3 a; b; c g g ; g ; g 11 7 4 6 7 m xno 5 r2 a; b g g ; g ; g ; g ; g 12 5 1 2 3 4 5 m nand4 4 a; b; c; d g g ; g ; g ; g ; g 13 9 4 6 7 8 9 m 3 oai21 a; b; g g g ; g ; g ; g 14 4 5 1 2 3 5

m + m m + m m + m m + m m + m ( )( )( )( )( ) 3 1 3 2 5 3 5 4 6 4 m + m m + m m + m m + m ( )( )( )( ) 7 6 8 7 9 8 10 6 m + m + m m + m + m m + m + m ( m + m m )( + m + m m )( + m + m ) 1 12 14 2 12 14 3 12 14 ( )( )( ) 14 4 5 12 14 9 10 13 m + m + m + m m + m + m ( )( ) 4 11 12 13 5 12 14 m + m + m m + m + m + m ( )( ) 6 11 13 7 10 11 13 m + m + m m + m + m ( )( ) : 8 10 13 9 10 13 例題の説明 • 各ノードgiがカバーされる • 各マッチごとに入力が存在するための条件 • 例: マッチm3を選ぶと、g1, g2の出力が実現されていないといけない。それには、マッチm1, m2が選ばれないといけない。つまり、m3→m1m2 • 回路の出力が実現されていないといけない • g5の出力を実現するために、(m5 + m12 + m14) • g9の出力を実現するために、(m9 + m10 + m13)

例題の解 • 58個のprime implicant • その内、コスト最小は: • m3’m5’m6’m7’m8’m9’m10’m12m13m14’ • つまり、m12(XOR2)とm13(NAND4)のみを使う • ゲートg4はm12にもm13にもカバーされていることに注意 • Treeに分解するとこの解は求まらない