Lecture 14: Wires

830 likes | 848 Vues

This lecture covers the basics of interconnect modeling, including wire resistance, wire capacitance, wire RC delay, crosstalk, and wire engineering techniques. It also explores the importance of wires in chip design, their impact on speed, power, and noise, and the use of multiple layers of wires.

Lecture 14: Wires

E N D

Presentation Transcript

Outline • Introduction • Interconnect Modeling • Wire Resistance • Wire Capacitance • Wire RC Delay • Crosstalk • Wire Engineering • Repeaters 14: Wires

Introduction • Chips are mostly made of wires called interconnect • In stick diagram, wires set size • Transistors are little things under the wires • Many layers of wires • Wires are as important as transistors • Speed • Power • Noise • Alternating layers run orthogonally 14: Wires

Wire Geometry • Pitch = w + s • Aspect ratio: AR = t/w • Old processes had AR << 1 • Modern processes have AR 2 • Pack in many skinny wires 14: Wires

Layer Stack • AMI 0.6 mm process has 3 metal layers • M1 for within-cell routing • M2 for vertical routing between cells • M3 for horizontal routing between cells • Modern processes use 6-10+ metal layers • M1: thin, narrow (< 3l) • High density cells • Mid layers • Thicker and wider, (density vs. speed) • Top layers: thickest • For VDD, GND, clk 14: Wires

Example Intel 90 nm Stack Intel 45 nm Stack [Thompson02] [Moon08] 14: Wires

Intel 45nm Stack 14: Wires

Intel 45nm Stack 14: Wires

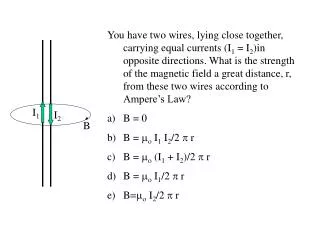

Interconnect Modeling • Current in a wire is analogous to current in a pipe • Resistance: narrow size impedes flow • Capacitance: trough under the leaky pipe must fill first • Inductance: paddle wheel inertia opposes changes in flow rate • Negligible for most wires 14: Wires

Impact of Interconnect • Reduce reliability • Affect performance • Increase tp • Increase energy dissipation • Cause the introduction of extra noise sources • Inductive effects usually ignored • Resistive effects ignored if wire is short • Interwire capacitance usually ignored if overlap is small • Wire capacitance is dominant 14: Wires

Wire Models Capacitance-only All-inclusive model

Fringing Capacitance 14: Wires

Fringing Capacitance • Some other formulas • This empirical formula is accurate to 6% for AR < 3.3 14: Wires

Wire Capacitance • Wire has capacitance per unit length • To neighbors • To layers above and below • Ctotal = Ctop + Cbot + 2Cadj 14: Wires

Capacitance Trends • Parallel plate equation: C = eoxA/d • Wires are not parallel plates, but obey trends • Increasing area (W, t) increases capacitance • Increasing distance (s, h) decreases capacitance • Dielectric constant • eox= ke0 • e0 = 8.85 x 10-14 F/cm • k = 3.9 for SiO2 • Processes are starting to use low-k dielectrics • k 3 (or less) as dielectrics use air pockets 14: Wires

M2 Capacitance Data • Typical dense wires have ~ 0.2 fF/mm • Compare to 1-2 fF/mm for gate capacitance 14: Wires

Capacitance of Dense Wires • An empirical equation is • Also, floating capacitors occur, which • Create noise • Affect performance 14: Wires

Wiring Capacitances • We typically use simple models for capacitance, given by 14: Wires

Diffusion & Polysilicon • Diffusion capacitance is very high (1-2 fF/mm) • Comparable to gate capacitance • Diffusion also has high resistance • Avoid using diffusion runners for wires! • Polysilicon has lower C but high R • Use for transistor gates • Occasionally for very short wires between gates 14: Wires

Wire Resistance • r = resistivity (W*m) • R = sheet resistance (W/) • is a dimensionless unit(!) • Count number of squares • R = R * (# of squares) 14: Wires

Choice of Metals • Until 180 nm generation, most wires were aluminum • Contemporary processes normally use copper • Cu atoms diffuse into silicon and damage FETs • Must be surrounded by a diffusion barrier 14: Wires

Contacts Resistance • Contacts and vias also have 2-20 W • Use many contacts for lower R • Many small contacts for current crowding around periphery 14: Wires

Copper Issues • Copper wires diffusion barrier has high resistance • Copper is also prone to dishing during polishing • Effective resistance is higher 14: Wires

Example • Compute the sheet resistance of a 0.22 mm thick Cu wire in a 65 nm process. Ignore dishing. • Find the total resistance if the wire is 0.125 mm wide and 1 mm long. Ignore the barrier layer. 14: Wires

Skin Effect 14: Wires

Skin Effect • Define a skin depth, d, where the current falls to 1/e of its nominal value. • Here, m is the permeability of the surrounding dielectric and has a typical value of approximately 4p X 10-7 for all dielectrics. • For Al at 1 GHz, d = 2.6mm. • To see the effect, assume a rectangular wire. • Assume that the current flows only in the skin as defined above 14: Wires

Skin Effect • The cross section is given by H W 14: Wires

Skin Effect • Using this cross sectional area, • We can define a frequency fs where the skin depth is half the highest dimension of the conductor. • It is not meaningful to increase the dimensions beyond that point for that frequency. 14: Wires

Skin Effect • For Al in SiO2, at 1GHz fs, the largest dimension should be 5.2mm. • Actual results show 30% increase in R due to skin effect for a 20mm wire and 2% for a 1mm wire. • One other thing to note is that the actual frequency of the square wave should not be used. • A sine wave whose rise and fall times equal to the rise and fall times of the square wave will give more accurate results. • For 20% - 80% rise and fall, the equivalent frequency is given by 14: Wires

Skin Effect • As another example, choose copper in SiO2 with 20ps edge rates. • f=5.8GHz, d = 0.99mm • Note that the resistivity of metals drops at very low temperatures. • For example, an order of magnitude improvement at 77K (liquid nitrogen). 14: Wires

Inductance • We will ignore inductance in this course • Inductance causes voltage variations • Inductance causes extra impedance. • Remember where • c: capacitance per unit length • l: inductance per unit length • e: permittivity of the surrounding dielectric • m: permeability of the surrounding dielectric 14: Wires

Inductance • Also, remember that 14: Wires

Inductance • How do we use this information? • From a previous table, 14: Wires

Inductance • Using • Equating the impedances, Z = wl • For a 1mm wide wire, r = Z at 30GHz. • Inductance is not an issue for now. • Typically, lower level metals are microstrips whose inductances are given by 14: Wires

Inductance • On-chip inductance is important for wires where the speed of light flight time is longer than either the rise times of the circuits or the RC delay of the wire. • This can be expressed as 14: Wires

Inductance 14: Wires

Inductance 14: Wires

Lumped Element Models • Wires are a distributed system • Approximate with lumped element models • 3-segment p-model is accurate to 3% in simulation • L-model needs 100 segments for same accuracy! • Use single segment p-model for Elmore delay 14: Wires

Wire RC Delay • Estimate the delay of a 10x inverter driving a 2x inverter at the end of the 1 mm wire. Assume wire capacitance is 0.2 fF/mm and that a unit-sized inverter has R = 10 KW and C = 0.1 fF. • tpd = (1000 W)(100 fF) + (1000 + 800 W)(100 + 0.6 fF) = 281 ps 14: Wires

Wire Energy • Estimate the energy per unit length to send a bit of information (one rising and one falling transition) in a CMOS process. • E = (0.2 pF/mm)(1.0 V)2 = 0.2 pJ/bit/mm = 0.2 mW/Gbps 14: Wires