الکترونیک دیجیتال منطق NMOS

Amirkabir University of Technology Computer Engineering & Information Technology Department. الکترونیک دیجیتال منطق NMOS. دکتر سعید شیری. مقدمه.

الکترونیک دیجیتال منطق NMOS

E N D

Presentation Transcript

Amirkabir University of TechnologyComputer Engineering & Information Technology Department الکترونیک دیجیتالمنطق NMOS دکتر سعید شیری

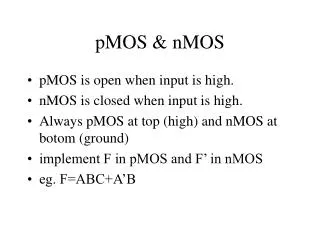

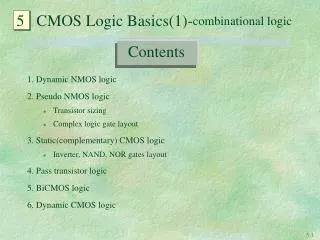

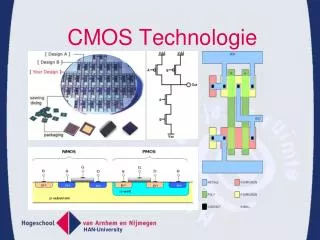

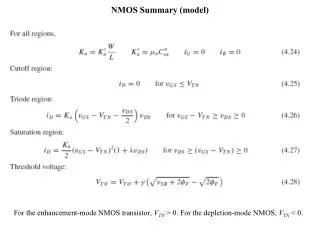

مقدمه • در منطق NMOS فقط از ترانزیستورهای n-channel استفاده میشود. بعلت اندازه کوچک ترانزیستورهای MOSFET مدارات ساخته شده با این منطق را میتوان بسیار مجتمع کرد. • ایراد اطلی این منطق توان مصرفی بالا در حالت stand-by است ( مقدار آن با مدارات دوقطبی قابل مقایسه است). • پردازنده ای اولیه تماما با این منطق ساخته شده بودند. با این وجود مدارات CMOS بدلیل مصرف پائین در اغلب کاربردها جایگزین NMOS شدند. • در حال حاضر NMOS در حافظه های پیشرفته مورد استفاده قرار میگیرد. حافظه های DRAM از یک ترانزیستور NMOS و یک خازن برای هر بیت استفاده میکنند

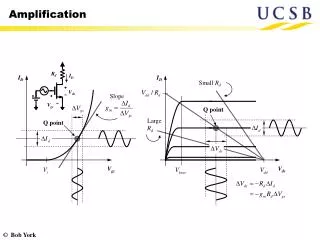

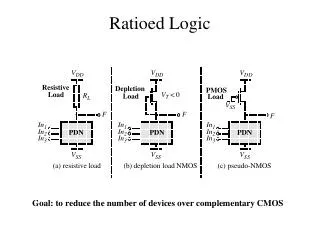

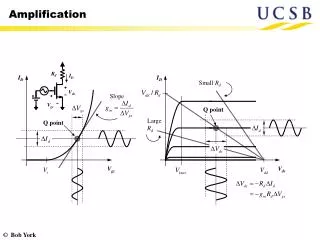

معکوس کننده NMOS • مدارات NMOS از یک بار و تعدادی سوئیچ NMOS ساخته میشود. در ساده ترین حالت یک مقامت بعنوان مدار pull-up استفاده میشود. در بخی مدارت مدار pull-up نیز از ترانزیستور ساخته میشود. • در شکل روبرو مدار یک معکوس کننده دیده میشود که در آن ترانزیستور یک تقویت کننده سورس مشترک است که در ناحیه قطع و تریود کار میکند. • وقتی ورودی در منطق صفر است، ترانزیستور در ناحیه قطع بوده و خروجی برابر با VDD و منطق یک میشود. وقتی ورودی در منطق یک قرار میگیرد ترانزیستور وارد ناحیه خطی شده و بصورت یک مقاومت عمل میکند. در این حالت ولتاژ خروجی کمتر از ولتاژ آستانه سوئیج مرحله بعد خواهد بود. • ایراد این مدار: • از آنجائیکه برای ساخت ترانزیستور به سطح بسیار بزرگتری از تراشه مورد نیاز است نمیتوان تعدادی زیادی از آنها را در یک مدار مجتمع جای دارد .

حذف مقاومت • اگر بجای مقاومت از یک ترانزیستور افزایشی استفاده شود میتوان مدار pull-up را با همان روش ساخت بقیه ترانزیستور ها ساخته و تعداد فرایندهای لازم برای ساخت ویفر را کاهش داده و هزینه مدار را کم کرد. • ایراد اصلی این مدار کاهش مقدار تغییرات ولتاژ خروجی است. یعنی بجای VDD قبلی به VDD-VT کاهش می یابد. • برای رفع این نقیصه میتوان از ترانزیستور تخلیه ای برای مدار pull-up استفاده نمود. این ترانزیستور میتواند با VGS=0 نیز روشن شود. این روش عمده ترین روش ساخت مدارات NMOS است.

مشخصه انتقال ولتاژ • وقتی ورودی مدار مقابل در منطق صفر باشد ترانزیستور سوئیچ قطع بوده و جریان ID ترانزیستور بار صفر خواهد بود لذا این ترانزیستور در ناحیه مقاومتی خود عمل خواهد نمود. درنتیجه VDS =0 خواهد شد. VOH=VDD • بازای ورودی VIN=VDD ترانزیستور سوئیچ در ناحیه اهمی و ترانزیستور بار در ناحیه اشباع قرار میگیرند. مقدار جریان دو ترانزیستور را اگر یکسان در نظر بگیریم داریم: • با حل این معادله ولتاژ خروجی بصورت زیر بدست می آید. • مقدار + در این رابطه غیر قابل قبول بوده و مقدار ولتاژ خروجی به نسبت ضرائب KL ,Ko بستگی دارد.

تعیین ولتاژ ورودی پائین • برای تعیین VIL مدار فوق فرض میشود که ترانزیستور سوئیچ در اشباع باشد و ترانزیستور بار در ناحیه اهمی. در اینصورت مقادیر جریان دو ترانزیستور بصورت زیر خواهند بود. • با مساوی قرار دادن آنها داریم: بنا به تعریف VIL در محلی تعیین میشود که شیب منحنی مشخصه 1- باشد:

تعیین ولتاژ VIH • به روش مشابهی میتوان مقدار ولتاژ VIH را تعیین نمود. در اینحالت فرض میشود که ترانزیستور سوئیچ در ناحیه اهمی و ترانزیستور بار در ناحیه اشباع قرار داشته باشد. بعلت ثابت بودن IDL در نهایت خواهیم داشت

مثال 1 • یک معکوس کننده NMOS با بار تخلیه ای طراحی کنید که با مقادیر زیر کار کند: VDD=2.5 V , VTO=0.6 V, VTL=-0.3 V • برای فرایند ساخت از تکنولوژی 0.5um با tox=7 nm و Un= 580 cm2/v در نظر بگیرید. • ترانزیستور باید طوری طراحی شود که مقدار VOL از مقدار VTO به مراتب کوچکتر باشد. با انتخاب VOL=0.3 V میتوان پارامترهای ترانزیستور را تعیین نمود. • برای داشتن عملکرد بهینه در شرایط پویا باید هر دو ترانزیستور با طول کانال مینیمم ساخته شوند.

مثال 2 • ولتاژهای مهم منحنی مشخصه انتقال ولتاژ گیت زیر را بدست آورید:

مثال 3 • منحنی مشخصه انتقال ولتاژ گیت زیر را بدست آورید: • میتوان مشخصه انتقال ولتاژ را بصورت نقطه به نقطه با معادل قرار دادن جریان درین ترانزیستورها و حل معادله ولتاژ خروجی بدست آورد. • برای اینکار با استفاده از جدول زیر میتوان حالت کاری هر یک از ترانزیستور ها را تعیین نمود.

ادامه مثال 3 • بازای Vin <0.5 ترانزیستور بالائی در ناحیه خطی و ترانزیستور پائینی در ناحیه قطع خواهد بود. • بازای 0.5 <= Vin <= Vout+ 0.50 ترانزیستور پائینی در ناحیه اشباع و ترانزیستور بار در ناحیه خطی خواهد بود. برای ترانزیستور اشباع میتوان نوشت:

ادامه مثال 3 • برای حالتی که ترانزیستور بار اشباع و ترانزیستور پائینی خطی است داریم: • معادلات فوق را میتوان بصورت نقطه به نقطه رسم نمود.

ادامه مثال 3 • شکل مقابل مشخصه حاصل را نشان میدهد. • در جدول زیر برخی از نقاط میانی نشان داده شده است

توان اتلافی • در مدارات NMOS توان استاتیک قسمت عمده توان مصرفی گیت را تشکیل میدهد. • وقتی خروجی در منطق یک است مقدار توان مصرفی اندک و برابر است با: • برای خروجی صفر ترانزیستور بار اشباع بوده وداریم: • از اینرو مقدار توان مصرفی برابر است با:

توان مصرفی • مقدار توان مصرفی به سرعت سوئیچینگ مدار بستگی دارد با اینحال برای duty cycle برابر با %50 مقدار متوسط توان مصرفی را میتوان بصورت زیر نوشت: • برای کاهش توان مصرفی میتوان VDD و یا مقدار K را کاهش داد. • کم کردن K میتواند بر فرکانس کاری مدار تاثیرگذار باشد

توان مصرفی • برای محاسبه توان مصرفی AC میتوان از شکل زیر استفاده نمود که در آن کل خازن موجود در مسیر خروجی یکپارچه شده است. • میزان انرژی مربوط به یک سیکل یعنی تغییر خروجی از صفر به یک و سپس از یک به صفر برابر است با: • اگر از جریان ترانزیستور pull down در هنگام تغییر خروجی از صفر به یک صرف نظر شود داریم: • از اینرو توان AC مصرفی برابر است با: • در این رابطه f فرکانس سوئیچینگ ترانزیستور است که خود درصدی از فرکانس کلاک مدار Fclk است. • با جمع مقدار توان AC و توان استاتیک کل مقدار توان مصرفی گیت بصورت زیر میشود.

تاخیر انتشار • برای محاسبه تاخیر انتشار tPLH فرض کنید در لحظه t=0 ورودی باندازه ای کاهش یافته باشد که ترانزیستور پائینی قطع باشد. از آنجائیکه ترانزیستور بار در ناحیه اشباع قرار خواهد گرفت: • لذا ولتاژ دو سر خازن از طبق رابطه زیر تغییر خواهد نمود: • طبق تعریف داریم: • از اینرو • این رابطه نشان میدهد که تاخیر انتشار با ظرفیت خازنی بار نسبت مستقیم و با مقدار جریان دهی ترانزیستور بار یعنی مقدار KL نسبت معکوس دارد.

تاخیر انتشار • برای محاسبه تاخیر انتشار tPHL فرض کنید در لحظه t=0 ورودی باندازه ای افزایش یافته باشد که ترانزیستور پائینی قطع باشد. از آنجائیکه ترانزیستور بار در ناحیه خطی و ترانزیستور پائینی در ناحیه اشباع باشد: • بدلیل وجود رابطه مرتبه 2 بین جریان IL و ولتاژ خروجی گرفتن مشتق از آن محاسبات را مشکل میکند. اگر کمی خطا پذیرفته شده و از این جریان صرف نظر شود میتوان تاخیر انتشار را فقط از طریق جریان ترانزیستور پائینی محاسبه نمود. • این رابطه نیز نشان میدهد که تاخیر انتشار با ظرفیت خازنی بار متصل به گیت نسبت مستقیم و با K نسبت عکس دارد. همچنین این تاخیر با ولتاژ تغذیه نیز نسبت عکس دارد.

مثال • مشاهده میشود که tPLH به مقدار 300 بار بزگتر ازtPHL است. • برای یکسان کردن تاخیر انتشار میتوان نسبت KL/KO را افزایش داد و یا اینکه VTL را منفی تر نمود. • هر یک از این تغییرات مقدار VOL را افزایش خواهد داد. لذا برای انجام آنها باید ویژگی های مشخصه انتقال ولتاژ را ملاحظه نمود.

Fan-Out • برای تعیین Fan-out گیت های NMOS بجای مشخصه های استاتیکی آن از ویژگی های دینامیکی استفاده میشود. زیرا اگر یک گیت NMOS به گیتهای مشابهی وصل شود تنها جریانی که از خروجی کشیده خواهد شد جریان نشتی گیت ترانزیستور بعدی است که قابل چشم پوشی است. • اما گیت ترانزیستور بعدی یک بار خازنی خیلی برزگ به همراه دارد که باعث مشود تا تاخیر انتشار مدار زیاد شود. از اینرو مقدار Fan-out از روی مقدار تاخیر انتشار قابل قبول بدست می آید. ( معمولا تاخیر انتشار قابل قبول حدود %5 پریود کلاک سیستم تعیین میشود)

Fan-Out • برای تعیین Fan-out میتوان فرضیات زیر را در نظر گرفت: • حداکثر مقدار تاخیر انتشار از قبل توسط طراح تعیین شده است. • تاخیر انتشارtPLH خیلی بیشتر از تاخیرtPHL انتشار است. • خازن معادل گیت های بار را میتوان با مقدار NCOX تقریب زد. • در اینصورت خواهیمداشت: • CIN خازن ورودی گیت NMOS است که میتوان آنرابصورت زیر تقریب زد: • برای کاربردهای فرکانس بالا Fan-out باید حداقل برابر 10 باشد.

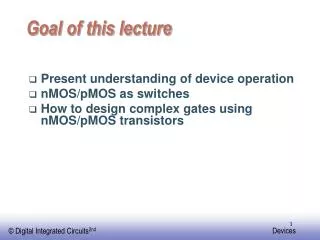

ساخت گیت NOR با منطق NMOS • گیت NOR با موازی قرار دادن ترانزیستور ها بدست می آید. • اگر سیگنال منطقی صفر به همه وردیها اعمال شود همه ترانزیستورها قطع بوده و خروجی در منطق یک قرار میگیرد. در غیر اینصورت حداقل یکی از ترانزیستورهای پائینی در ناحیه خطی قرار گرفته و خروجی در منطق صفر قرار میگیرد.

ساخت گیت NAND با منطق NMOS • برای بدست آوردن منطق NAND ترانزیستورهای پائینی بصورت سری با هم قرار میگیرند. برای اینکه این مدار بتواند VOL یکسانی با یک گیت NOT داشته باشد باید نسبت های آن در N یعنی تعداد ورودیها ضرب شود. • با برزگتر کردن نسبت های ترانزیستورها، سطح بزرگتری از ویفر لازم خواهد بود که چندان مطلوب نیست. از اینرو تعداد ورودی های این گیت محدود خواهد بود. • علاوه بر آن ویژگی های دینامیکی ترانزیستور نیز بدتر خواهد شد. • از اینرو گیت NOR بر گیت NAND ترجیح داده میشود.

پیاده سازی توابع عمومی با منطق NMOS • برای پیاده سازی هر منطقی باید دقت نمود که ترانزیستورهائی که با هم بصورت سری قرار میگیرند باید با ضریب M بزرگتر ساخته شوند.