The Silicon Laboratories C8051F020

120 likes | 300 Vues

The Silicon Laboratories C8051F020. Enhanced 8051 Part 3 Digital to Analog Conversion (DAC). Digital to Analog Conversion. 0001 0010. Digital Signals:. 04, 00, 06, 12, 1D, 22, 21…. Analog Signal. ideal. actual. Digital to Analog Conversion. Two general types

The Silicon Laboratories C8051F020

E N D

Presentation Transcript

The Silicon Laboratories C8051F020 Enhanced 8051 Part 3 Digital to Analog Conversion (DAC) ECE/CS-352: Embedded Microcontroller Systems

Digital to Analog Conversion 0001 0010 Digital Signals: 04, 00, 06, 12, 1D, 22, 21…. Analog Signal ideal actual ECE/CS-352: Embedded Microcontroller Systems

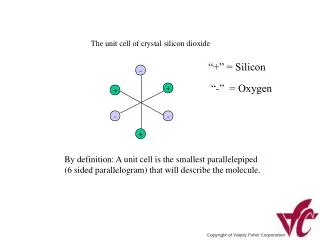

Digital to Analog Conversion • Two general types • Weighted D/A Converter (4-bit example) R digital input Q3 Q2 Q1 Q0 analog output 2R 4 Rout register 4R 1111 8R 1100 1000 0100 0000 ECE/CS-352: Embedded Microcontroller Systems

Digital to Analog Conversion Ladder D/A Converter (4-bit example) Q3 Q2 Q1 Q0 analog output 2R digital input 4 R 1111 register 2R 1100 R 2R 1000 R 2R 0100 2R 0000 ECE/CS-352: Embedded Microcontroller Systems

Digital/Analog Converters in C8051F020 DAC0 and DAC1 (identical) When disabled, output is high impedance Data registers 12 bit digital value ECE/CS-352: Embedded Microcontroller Systems

DAC0CN: DAC Control Register DAC Output Scaling/Justification DAC Enable 0 = disable 1 = enable • DAC Mode • 00: DAC updates occur on a write to DAC0H. • 01: DAC updates occur on Timer 3 overflow. • 10: DAC updates occur on Timer 4 overflow. • 11: DAC updates occur on Timer 2 overflow. ECE/CS-352: Embedded Microcontroller Systems

DAC Output Scaling/Justification ECE/CS-352: Embedded Microcontroller Systems

DAC Registers • In mode 00 (default), analog output is updated on a write to DAC0H (or DAC1H) DAC0H (8) DAC0L (8) DAC1H (8) DAC1L (8) Example: ECE/CS-352: Embedded Microcontroller Systems

Conversion Synchronization • Use Timer overflows to synchronize DAC when it is important to have smooth output waveforms. Using software loops which may be interrupted. Using timer overflows. ECE/CS-352: Embedded Microcontroller Systems

Output Voltage Swing 0 analog range Vref – 1 lsb 000h digital range FFFh (4095) ECE/CS-352: Embedded Microcontroller Systems

Reference Voltage • Can be an external voltage on pin VREFD • Can be the internal reference voltage VREF (2.4V) ECE/CS-352: Embedded Microcontroller Systems

Configuring VREFD REF0CN • BIASE: ADC/DAC Bias Generator Enable Bit. • (Must be ‘1’ if using ADC or DAC). • 0: Internal Bias Generator Off. • 1: Internal Reference Buffer On. Internal voltage reference is driven on the VREF pin. • REFBE: Internal Reference Buffer Enable Bit. • 0: Internal Reference Buffer Off. • 1: Internal Reference Buffer On. ECE/CS-352: Embedded Microcontroller Systems