Advanced Processor Design Concepts: Enhancing Performance through Modern Engineering

Explore the dynamic-static interface (DSI) in processor design, from pipelines to caches, memory hierarchy, parallelism, and more. Learn about performance simulation methods and strategies for mitigating hazards in deep pipelines. Get insights into advanced processor architectures.

Advanced Processor Design Concepts: Enhancing Performance through Modern Engineering

E N D

Presentation Transcript

Conceptuall illustration of possible placement of DSI in ISA design

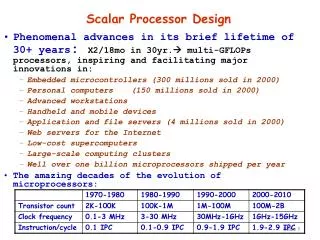

Performance simulation metods Trace-driven simulation Execution-driven simulation

Superpipelined MIPS R4000 8-stage pipeline

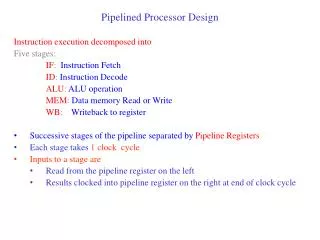

Pipeline example 4-stage 11-stage

Impact on ALU, Load, and Branch penalties with increasing pipeline depth

Parallel pipeline - examples 5-stage Pentium parallel pipeline s=2 5-stage i486

Interpipeline-stage buffers single-entry buffer multi-entry buffer multi-entry buffer with reordering

Dynamic pipeline with reservation stations and reorder buffer