DIGITAL IC COUNTERS

DIGITAL IC COUNTERS. Lecture 7. Consider the timing diagram for the 4-bit counter circuit. There is a delay or ripple effect on the output transitions, each output being delayed from the previous due to the propagation delay through the flip-flop.

DIGITAL IC COUNTERS

E N D

Presentation Transcript

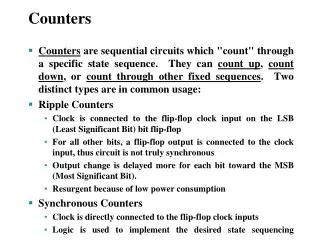

DIGITAL IC COUNTERS Lecture 7

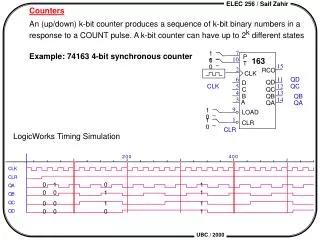

Consider the timing diagram for the 4-bit counter circuit. There is a delay or ripple effect on the output transitions, each output being delayed from the previous due to the propagation delay through the flip-flop. When all the outputs do not become valid “at once”, the circuit is ASYNCHRONOUS. These circuits are generally identified by the different flip-flops being clocked by different signals. This counter circuit is often called a RIPPLE COUNTER. Clock Q0 Q1 Q2 Q3 Valid Output Asynchronous and Synchronous Circuits

In many circuits it is necessary to ensure that all outputs change simultaneously or SYNCHRONOUSLY. This can be achieved by clocking all the flip-flops with the same clock signal. Look at a Synchronous 4-bit counter circuit This circuit must produce synchronous outputs because all the flip-flops are clocked by the same signal. Clock Q0 Q1 Q2 Q3 C0 Q0 C1 Q1 C2 Q2 C3 Q3 D Q D Q D Q D Q Synchronous Circuits

Clock X0 Y0 Combinatorial Circuit X1 Y1 Synchronous Counter: A Closer Look To look at how this might work, we will first simplify it to a 2-bit counter, ie: 00->01->10->11->00->… At startup the outputs are both 0. These feed back into the comb. cct to put values of 1 for Y0 and 0 for Y1, ready for the next clock pulse. The clock “strikes”: the 1 and 0 flow through to X0 and X1, but again feed back to the comb. cct which places 0 onto Y0 & 1 onto Y1 (ready for the next clock). The clock “strikes”: the 0 and 1 flow through to X0 and X1, but again feed back to the combinatorial circuit which places 1 onto Y0 & 1 onto Y1. The clock “strikes”: the 1 and 1 flow through to X0 and X1, but again feed back to the combinatorial cct which places 0 onto Y0 & 0 onto Y1. Clock: The X’s are both 0 & the Y’s are 1 & 0, we’re back to the start.

S0 S1 S2 S3 00 01 10 11 Synchronous Counter as a State Machine How is this counter working? The outputs are part of the inputs for the next Y0 and Y1 pair, ie the circuit is remembering its past output. That is, it’s behaving like a state machine. Sometimes it is better to model the behaviour of a machine rather than what it actually looks like. The PALASM system allows us to specify a machine as a state machine and it will program the circuits for us. So that is the direction we must now take: State Machines and The PALASM System Section 3. X1 X0

What's A 7-Segment Display? A 7-segment display is a package with 7 bar-shaped LEDs arranged to allow the display of many useful digits and some letters. Each segment (labeled A-G) contains an LED which may be individually controlled. DP is an eighth LED, the decimal point.

Common cathode means that each segment's cathode is connected to common pins – 3 & 8, allowing the anode of each to be connected to the controller.

Limiting resistor Computation RS= = 230