Lógica Seqüêncial

200 likes | 445 Vues

Lógica Seqüêncial. Bruno Silvério Costa. 1-Introdução. Os circuitos digitais podem ser classificados em dois grupos, dependendo da sua forma de construção: Circuitos Combinacionais Circuitos Seqüênciais. 2-Circuitos combinacionais.

Lógica Seqüêncial

E N D

Presentation Transcript

Lógica Seqüêncial Bruno Silvério Costa

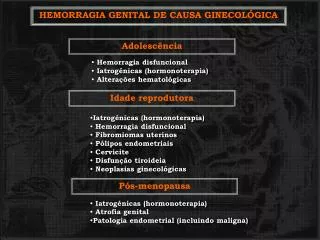

1-Introdução • Os circuitos digitais podem ser classificados em dois grupos, dependendo da sua forma de construção: • Circuitos Combinacionais • Circuitos Seqüênciais

2-Circuitos combinacionais • São circuitos cujos valores de saída dependem exclusivamente da entrada e da função lógica realizada pelo circuito.

3-Circuitos Seqüênciais • São circuitos que, além dos valores de entrada e da função do circuito, utilizam o estado anterior para determinar a saída.

habilita D(t) Q(t) 4-Latches • Um latch (trinco) é um elemento lógico que pode acompanhar as variações do dado e transferir estas mudanças para uma linha de saída. • Representação genérica de um latch: • Devido sua independência das entradas, um latch pode servir para ‘armazenar’ (registrar ou memorizar) um bit lógico. • O armazenamento da informação é possibilitado através de um circuito biestável (dois possíveis estados estáveis), no qual Q=0 ou Q=1 pode ser armazenado na célula.

S Q \Q R entradas saídas 5-Latch SR • O latch set-reset (SR) é elemento biestável, transparente, ou seja, sensível às variações das entradas. • Um latch SR tem duas entradas chamadas de S e R e uma saída chamada de Q. • O valor complementar \Q da saída também é fornecido. • O nome do elemento é obtido das definições das duas operações básicas: • Set (S), na qual a saída é forçada para o valor Q=1 • Reset (R), na qual a saída é forçada para o valor Q=0

D Q’ Q D Q 0 0 1 1 8-LatchD • Um Latch tipo D é um Latch RS com as entradas RS interligadas através de uma inversora.

9-Flip-Flops • Um Flip-Flop é um latch controlado pelo valor do sinal de clock a ele submetido. • Um flip-flop é um circuito digital básico que armazena um bit de informação. • A saída de um flip-flop só muda de estado durante a transição do sinal de clock.

10-Flip-FlopsRS Síncrono (1) • Tem uma entrada chamada clock, além das R e S. • O clock faz com que o flip-flop RS atualize seus estados. S’ R’

10-Flip-Flops RS Síncrono (2) • Com o clock em nível zero (CK=0), as saídas anteriores são mantidas. • Com o clock em nível um (CK=1), o flip-flop RS síncrono opera como um flip-flop RS básico. ‘ ‘ FlipFlop RS Sinc R Q CK Q’ S

11-Flip-Flop JK(1) • Tipo de flip-flop RS aprimorado, onde a indeterminação lógica foi removida. RS síncrono

11-Flip-Flop JK(2) • Tabela da Verdade QA = 0 0 1 = 1 = Q’A Q’A = Q’A

12-Flip-Flop Mestre-Escravo(1) • Possui este nome devido aos dois blocos internos com os quais ele é formado • Estes dois blocos representam dois circuitos separados de latch. • O latch mestre é utilizado para aceitar a entrada do bit de dado A no flip-flop • O valor de A é armazenado no mestre e, então, transferido para o escravo em um tempo posterior. • Ambas as entradas são sincronizadas pelo sinal de clock Q Q=A A B A A Mestre (Ativo) Mestre Escravo (Ativo) Escravo Mestre ativo Escravo ativo

12-Flip-Flop Mestre-Escravo(2) • Para eliminar a oscilação do flip-flop JK, foram combinados dois flip-flops RS como no circuito a seguir, denominado flip-flop JK Master-Slave (Mestre-Escravo). (Mestre JK) (Escravo SR)

13-Flip-Flop D (JK tipo D) • A partir de um flip-flop JK, podemos construir um tipo particular de flip-flop através da conexão ilustrada abaixo, obtendo um flip-flop tipo D.

14-Flip-Flop T (JK tipo T) • A partir de um flip-flop JK, podemos construir um outro tipo particular de flip-flop através da união de suas entradas J e K (ilustrada abaixo), obtendo um flip-flop tipo T. 1 0 0 1

15-Aplicações dos Flip-Flops • Com a utilização dos flip-flops, podemos construir circuitos: • divisores de freqüência; • registradores de deslocamento unidirecionais e bidirecionais • contadores assíncronos e síncronos • Unidades de controle • Memórias • Etc...