Extending and Analyzing RISC Processor using Bluespec mid-term presentation

18/3/2013. Performed By: Yahel Ben- Avraham and Yaron Rimmer Instructor: Mony Orbach Bi- semesterial , 2012 - 2013. Extending and Analyzing RISC Processor using Bluespec mid-term presentation. Reminder - Project goals. Goal: Extending and analyzing RISC Processor using Bluespec

Extending and Analyzing RISC Processor using Bluespec mid-term presentation

E N D

Presentation Transcript

18/3/2013 Performed By: Yahel Ben-Avraham and YaronRimmer Instructor: MonyOrbach Bi-semesterial,2012 - 2013 Extending and Analyzing RISC Processor using Bluespecmid-term presentation

Reminder - Project goals • Goal: Extending and analyzing RISC Processor using Bluespec • Part A: • Studying the working environment, BSV language and the basic processor implementation. • Logical design of processor modifications • Theoretical analysis of performance

Work flow & progress • Learning Bluespec • Setting up the environment* • Study the simple RISC processor implementation • Assessing modification options. • Logical design of modifications. • Performance analysis and assessing of functional changes (theoretically). • Implementing and testing*.

Modifications • Extend the basic RISC processor: • 1st phase: Extend the pipe. • 2nd phase: Add functional capabilities.

The working environment • Will use platform by Shai and Dani. • Allowing us to focus on the processor. • The platform enables: • Synthesis of design to FPGA via Direct PC. • Cycle level control using COP. • Reading and writing to memories via JTAG.

Pipe expansion • Goal: 5-stage pipeline • Pipe stages: Fetch, Decode, Execute, Memory, WriteBack • Including Data forwarding, Hazard detection.

Other capability expansions • Branch prediction • 1-bit / 2-bit saturated counter • History bits • BTB • Cache • Replacement policies (LRU…) • Read/write policies • Indexing

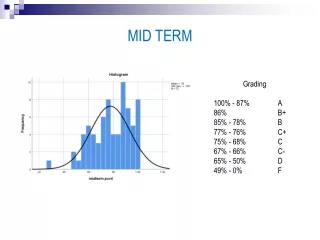

Performance analysis • Assess the processor’s capabilities • Instructions per cycle • Throughput • Latency • Miss rates • More