WRR ARBITER Mid-term Presentation

WRR ARBITER Mid-term Presentation. Students: Ofer Sobel Guy Marcus Supervisor: Moshe Porian. 11/1/11. Project Goal. Implementing a WRR ARBITER on an FPGA Implementation will be to Altera Cyclone® II 2C35 FPGA located on an Altera DE2 board. Project steps.

WRR ARBITER Mid-term Presentation

E N D

Presentation Transcript

WRR ARBITERMid-term Presentation Students: OferSobel Guy Marcus Supervisor: Moshe Porian 11/1/11

Project Goal Implementing a WRR ARBITER on an FPGA Implementation will be to Altera Cyclone® II 2C35 FPGA located on an Altera DE2 board

Project steps • Determining specifications • Architecture characterization • Conceptual design • VHDL implementation • Verification • Synthesis • Real-Time testing

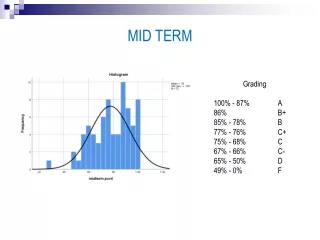

Arbitration - wave • Tick time: every 5 clocks • Weights: • Filtered requests

Arbiter features • External/ internal request muxing • Grant history tracking • Status message initiation

Testability Tested modules: • RX Path • TX Path • Controller and Peripherals • Arbiter module • Top

Simulation environment Input file:

Simulation environment Output Log:

Test Plan (Arbiter Module) • Reset and registers test • Steady state arbitration test • Dynamic arbitration test • Mode test • Filter test • Configuration switch test • Random arbitration test • Functional test