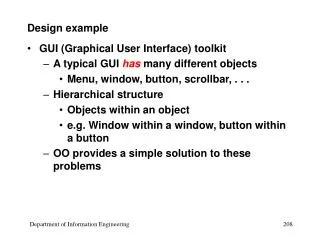

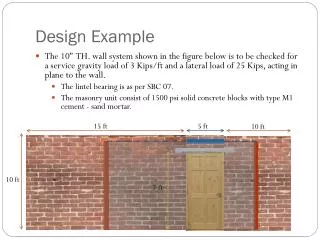

Design example

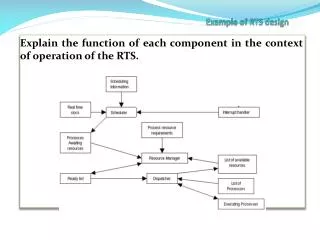

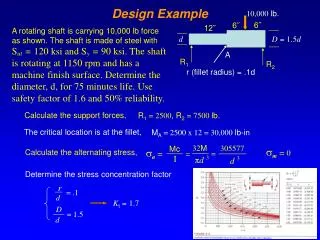

Design example. Binary Multiplier. Block diagram. ASM chart. Numerical example. Control logic. Control block. L is required for loading the sum into register A if Q 0 =1 while in state T 2. State assignment. State table for control circuit. Logic diagram of control. One F.F. per state.

Design example

E N D

Presentation Transcript

Design example Binary Multiplier

Control block • L is required for loading the sum into register A if Q0=1 while in state T2

HDL description module mltp(S,CLK,Clr,Binput.Qinput,C,A,Q,P) ; input S,CLK,Cir; input [4:01 Binput.Qinput; //Data inputs output C; output [4:0] A,Q; output [2:0] P; reg C; reg [4:0] A,Q,B; reg [2:0] P; reg [1:0] pstate, nstate; //control register parameter T0=2'b00, Tl=2'b01, T2=2'bl0, T3=2'bll; wire Z; assign Z = ~|P; //Check for zero always @(negedge CLK or negedgo Cir) if (~Clr) pstate = T0; else pstate <= nstate; always @(S or Z or pstate) case (pstate) T0: if (S) nstate = Tl; else nstate = T0; Tl: nstate = T2; T2: nstate = T3 ; T3: if (Z) nstate = TO; else nstate = T2; endcase HDL Example 8-5

always @(negedge CLK) case (pstate) TO: B <= Binput; //Input multiplicand Tl: begin A <= 5'b00000; C <= 1'b0; P <= 3~b101;//Initialize counter to n=5 Q <= Qinput;//Input multiplier end T2: begin P <= P - 3'bOOl; //Decrement counter if (Q[0]) {C,A} <= A + B; //Add multiplicand end T3: begin C <= 1'b0;//Clear C A <= {C,A[4:1]}; //Shift right A Q <= {A[0],Q[4:l]}; //Shift right Q end endcase endnodule

HDL Example 8-6 module test_mltp; reg S,CLK,Clr; reg [4:0] Binput,Qinput; wire C; wire [4:0] A,Q; wire [2:0] P; mitp mp(S,CLK,Clr,Binput,Qinput,C,A,Q,P), initiAl begin S=0; CLK=0; Clr=0; #5 S=l; Clr=l; Binput = 5'b10111; Qinput = 5'b10011; #15 S = 0; end initial begin repeat (26) #5 CLK = ~CLK; end always @(negedge CLK) $strobe("C=%b A=%b Q=%b P=%b time=%0d",C,A,Q,P,$time) endmodule Test bench