Register-Transfer Level Estimation Techniques for Switching Activity and Power Consumption

180 likes | 333 Vues

Register-Transfer Level Estimation Techniques for Switching Activity and Power Consumption. Anand Raghunathan, Sujit Dey, and Niraj K. Jha. Outline. Motivation RTL power estimation methodology Estimating glitching activity at the RT level RTL power models Experimental results. Motivation.

Register-Transfer Level Estimation Techniques for Switching Activity and Power Consumption

E N D

Presentation Transcript

Register-Transfer Level Estimation Techniques for Switching Activity and Power Consumption Anand Raghunathan, Sujit Dey, and Niraj K. Jha

Outline • Motivation • RTL power estimation methodology • Estimating glitching activity at the RT level • RTL power models • Experimental results

Motivation • 1.64mW with CSIM • 1.32mW with no gltich (19.5% under estimate) • 1.53mW with glitching activity and power estimation

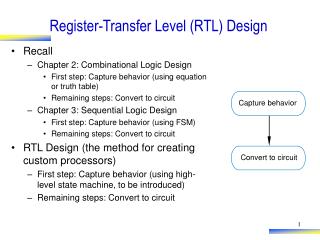

RTL power estimation methodology • First phase • Word- and bit-level • Mixed-level • High speed • Second phase • Zero-delay + gate-delay • Third phase • Build power models • Bit-level

Estimating glitching activity at the RT level • Models for glitch generation • Propagation through various components • Two sub sections • Glitching activity at the control signals • Glitch generation and propagation in data path

Glitching activity at the control signals • Using control expressions

Glitching activity at the control signals-Example 1 • S3 to S4 • x4↑and x3↓ • If x4 is later than x3 • 1-0-1 on contr[1] • Two conditions • Logic • Correlation between rising and falling transitions • Simultaneous occurrence • Temporal • Related to controlling value 0 1 1 0 1 0

Glitching activity at the control signals-Example 1 (cont.) • Logic conditions • At least one rising and at least on falling • At the gate’s input • No input assume a steady controlling value • Temporal conditions – AND for example • Earliest falling after the latest rising • An interval great than the gate’s inertial delay

Glitching activity at the control signals-Example 1 (cont.) • Glitch counter for each product term • Increment when two conditions satisfied • In each cycle • Not easy to know accurate manner • Pessimistic assumption • Whenever the logic conditions • Leads to over-estimates of glitching

Glitching activity at the control signals-Example 2 • contr[2]=x0+x1C11+x3C10 • Logic conditions • Case 1: Count(x1↓,C11↑)=15 • Case 2: Count(x1↑,C11↓)=20 • Case 3: Count(x3↓,C10↑)=35 • Case 4: Count(x3↑,C10↓)=30 • 100 estimated glitches; while 52 by CSIM

Glitching activity at the control signals-Example 2 (cont.) • Partial information • Toutputs of comparators > Tpresent state signals • Divide input into three group • Early • Late • Unknown ─ pessimistic approach

Glitching activity at the control signals-Example 3 • contr[2]=x0+x1C11+x3C10 • Logic conditions • Case 1: Count(x1↓,C11↑)=15 • Case 2: Count(x1↑,C11↓)=20 • Case 3: Count(x3↓,C10↑)=35 • Case 4: Count(x3↑,C10↓)=30 • 50 estimated glitches; while 52 by CSIM

Modeling glitch generation and propagation in data path blocks • Glitch generation and propagation in multiplexers • Mux_gl_gen[] • Ai(t), Bi(t), Seli(t), Ai(t-1), Bi(t-1), Seli(t-1)

RTL Power Models • Datapath • Controller

Datapath Power Models • Bit-level signal • Transition probabilities • Correlations • Glitching activity

Controller Power Models • Assume • 2-input AND • 2-input OR • Inverter