Generating RT-Level Verilog IP Documentation Based on VSIA and Automation Techniques

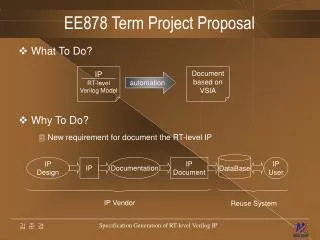

This document outlines a project proposal aimed at generating RT-level Verilog IP specifications utilizing automation techniques and methodologies based on VSIA standards. It details two key methods for specification generation: Method 1 involves extracting information from the IP documentation itself, including specification, block diagrams, and timing diagrams. Method 2 focuses on utilizing meta-comments within the Verilog code to clarify synthesis specifications. The goal is to enhance the documentation process for IP design and facilitate vendor reuse.

Generating RT-Level Verilog IP Documentation Based on VSIA and Automation Techniques

E N D

Presentation Transcript

IP RT-level Verilog Model Document based on VSIA automation New requirement for document the RT-level IP DataBase IP Design IP Documentation IP Document IP User IP Vendor Reuse System EE878 Term Project Proposal What To Do? Why To Do? Specification Generation of RT-level Verilog IP

Method 1 - Utilizing the Information extractable from IP itself Document Specification block diagram timing diagram . . . . (based on VSIA) IP RT-level Verilog model Verilog parser Internal Data Structure Extract Wanted Info DEVS based EE878 Term Project Proposal How To Do? Method 2 - Utilizing the meta comment Put information on comment section ex.) synthesis Specification Generation of RT-level Verilog IP