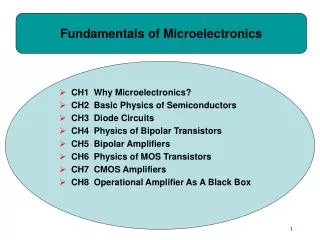

Microelectronics 2

In this lecture by Dr. Peter Ewen, we delve into the principles of abrupt junction diffusion and implantation as relevant to microelectronics. Topics include the abrupt junction model, dopant concentrations, and electric field equations for p-n junctions. The operation of Metal-Oxide-Semiconductor (MOS) transistors is explored, focusing on gate-controlled surface effects, threshold voltage calculations, and channel behavior in n-channel devices. The analysis covers device fabrication, characteristics, and performance, essential for engineering applications and semiconductor technology.

Microelectronics 2

E N D

Presentation Transcript

Electrical Engineering 2 Lecture 13 Microelectronics 2 Dr. Peter Ewen (Room G08, SMC; email - pjse)

The Abrupt Junction Diffusion Implantation Abrupt junction model NA Dopant concentration NA or ND Dopant concentration NA or ND p n p n xj xj ND ND Depth into wafer, x Depth into wafer, x ABRUPT JUNCTION LINEARLY-GRADED JUNCTION

junction - - - - - - - - - - - - - - - - - - - - + + + + + + + + + + + + + + + + + + + + - - + + - + - + - + - + - + - + - + - + n-type p-type + - + - + - + - + - + - + - + - + - + - -ve +ve The charges in the depletion region are those on the carriers and on the charged impurity ions fixed in the lattice. E depletion region Taking the sign of the charges into account: c = e(p – n + ND – NA) dE e dx = (p – n + ND – NA) For simplicity take n = 0 & p = 0 – the depletion approximation

Depletion region - - - - - - - - - - - - - - - - - - - - + + + + + + + + + + + + + + + + + + + + - - + + - + - + - + - + - + - + - + - + + - + - + - + - + - + - + - + - + - + - n-type p-type lp x=0 ln junction Charge density variation through a pn junction Charge density, c eND 0 Distance, x -eNA Fig. 76.2

To find the Electric Field For the p-type side we have: Poisson’s equation on p-type side Since NA is constant (abrupt junction) Since E = 0 outside the depletion region, i.e. at x Ip Similarly, for the n-type side:

To find the Potential The electric field, E, is defined by: For the p-type side we have: If we take the zero of potential to be at x = 0 then C' = 0.

- - - - - - - - - - - - - - - - - - - - + + + + + + + + + + + + + + + + + + + + - - + + - + - + - + - + - + - + - + - + + - + - + - + - + - + - + - + - + - + - n-type p-type lp x=0 ln eND Charge density, c 0 0 0 Distance, x -eNA Electric field, E E Distance, x Ep En Emax VB Vn Potential, V Vp Distance, x

MOS Transistor – Basic Structure Gate Source Drain n-channel device +Vg Metal Oxide Semiconductor SiO2 n+ n+ Channel p-type substrate Fig. 80

LECTURE 13 • Operation of the MOS transistor – gate-controlled surface effects • MOS fabrication – enhancement and depletion devices • MOS Pinch-off

- - - - - - - - - - - - - - + + + + + + + Gate-Controlled Surface effects drain SiO2 n+ metal gate n-channel device (enhancement) Fig. 81 p-type substrate holes source n+ acceptor ions electrons −ve voltage on gate +ve voltage on gate Charge QG Channel forms when the +ve voltage on the gate is greater than VT (threshold voltage) QA (A ≡ Accumulation) QA = -QG Distance (D ≡ Depletion) QD = -QG QD “Inversion” occurs QC + QC QG (C ≡ Channel)

drain Gate-Controlled Surface effects SiO2 p+ metal gate p-channel device n-type substrate Fig. 82 source p+ -ve voltage on gate with magnitude greater than VT Charge QC QD Distance QG

MOS Threshold Voltage • An n-channel polysilicon gate MOS transistor has the following features: • oxide thickness tox = 0.1 m • channel width W = 18 m • channel length L = 6 m • substrate doping NA = 5x1022 m-3 • oxide relative permittivity ox = 4 • EF − EV for substrate = 0.175 eV • Eg = 1.1 eV for Si • Determine the gate capacitance, Cg. • If the depth of the depletion region at VG = VT is • 0.14 m, how much of VT goes to creating QD?

oxide thickness tox= 0.1 m • channel width W = 18 m • channel length L = 6 m • substrate doping NA= 5x1022 m-3 • oxide relative permittivity ox = 4 • EF − EV for substrate = 0.175 eV • Eg = 1.1 eV for Si 1. MOS threshold voltage • Determine the gate capacitance, Cg. L SiO2 SiO2 SiO2 W Gate conductor (metal) insulator (oxide) conductor (silicon) Drain Drain Drain Source Source Source n+ n+ n+ n+ n+ n+ tox

_ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ • oxide thickness tox= 0.1 m • channel width W = 18 m • channel length L = 6 m • substrate doping NA= 5x1022 m-3 • oxide relative permittivity ox = 4 • EF − EV for substrate = 0.175 eV • Eg = 1.1 eV for Si Gate region of n-channel MOS (b) If the depth of the depletion region at VG= VT is 0.14 m, how much of VT goes to creating QD? VT +ve Gate SiO2 inversion layer of electrons _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ depletion region ionised acceptor atoms p-type substrate

The part of VT that goes into creating the depletion charge QD is therefore _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ depth of depletion region – 0.14 m • oxide thickness tox= 0.1 m • channel width W = 18 m • channel length L = 6 m • substrate doping NA= 5x1022 m-3 • oxide relative permittivity ox = 4 • EF − EV for substrate = 0.175 eV • Eg = 1.1 eV for Si Gate region of n-channel MOS VT +ve Gate SiO2 _ Depth _ _ _ W L p-type substrate

n-channel C.B. EC EF EV 0.175eV 1.1eV V.B. n-channel C.B. EC EV 1.1eV V.B. For effective inversion EF must be 0.175eV below EC in the n-type channel, i.e. the band diagram must move down by: (1.1 – 20.175)eV = 0.75eV. (c) If effective inversion occurs when the channel is as n-type as the wafer is p-type, determine an approximate value for VT. p-type substrate C.B. EC EF EV (1.1 – 20.175)eV = 0.75eV 1.1eV 0.175eV V.B.

MOS Fabrication Fig. 83 n-channel enhancement device donor diffusion Polysilicon Gate polycrystalline Si (“polysilicon”) Source Drain Al Al SiO2 n+ n+ “self-aligned” gate n+→ “+” indicates heavy doping p-type substrate (wafer) NA~ 1020 m-3

Gate Contact Gate contact made here n-channel device Source Drain SiO2 n+ n+ Fig. 84

MOS Fabrication n-channel depletion device Polysilicon Gate Source Drain Al Al SiO2 n+ n+ Implanted channel p-type substrate (wafer) NA~ 1020 m-3

n-channel enhancement device n-channel depletion device Polysilicon Gate Polysilicon Gate Source Drain Source Drain Al Al Al Al n+ n+ n+ n+ Implanted channel IDS IDS 0 VT VGS VT VGS 0 • Same considerations apply to p-channel devices.

MOS Pinch-off Fig. 85 n-channel enhancement device +8V +7V +7.5V 0V VT = 1 V gate source drain SiO2 -eE→ n+ n+ inversion layer depletion region p-type substrate Vox≥ VT everywhere between source and drain. Vox drops below VT at drain end – channel becomes interrupted or “pinched off”

Condition for pinch-off Fig. 86 n-channel enhancement device +8V +7V 7.5V gate 0V VT = 1 V VGS VGD source drain SiO2 n+ n+ VDS Vox is smallest at the drain end of the gate, hence pinch-off first occurs when VGD = VT G VGD VGD= VT VGS – VDS = VT VDS= VGS – VT D VGS VDS S Pinch-off first appears when: VDS= VGS – VT

Condition for pinch-off – all devices n-channel device p-channel device The channel will be pinched-off if the voltage difference across the oxide layer at the drain end of the channel (i.e. VGD) is less than VT The channel will be pinched-off if the voltage difference across the oxide layer at the drain end of the channel (i.e. VGD) is greater than VT gate gate drain drain VGD VGD VT +ve VT -ve n+ n+ n+ n+ VGD= VGS – VDS G • VGD > VT • VGS – VDS > VT VDS < VGS – VT • VGD < VT • VGS – VDS < VT VDS > VGS – VT D VGS VDS S

Conditions for pinch-off – all devices The channel will be pinched-off if: n-channel enhancement device VDS > VGS – VT n-channel depletion device p-channel enhancement device VDS < VGS – VT p-channel depletion device

gate source drain n+ n+ gate source drain n+ n+ ID VDS>VGS-VT VDS=VGS-VT VDS Effect of pinch-off on the current through the device

2. Pinch-off The terminal voltages for an n-channel enhancement MOS transistor with VT = 1V are given below. Is the channel pinched off? VG = 5V VD = 4.5V VS = 3V

To see if the channel is pinched off we need to compareVDS with VGS – VT . Device is n-channel so if VDS > VGS – VT the channel is pinched off VDS < VGS – VT the channel is not pinched off VDS is the voltage on the drain with respect to the source: VDS = VD – VS = 4.5 – 3 = 1.5V VGS is the voltage on the gate with respect to the source: VGS = VG – VS = 5 – 3 = 2V VGS – VT = 1, hence VDS > VGS – VT and so the channel is pinched off. +5V +7V 4.5V 3V VT = 1 V VGS gate source drain n+ n+ VDS

Summary SiO2 n+ metal n-channel device (enhancement) gate p-type substrate • MOS OPERATION • n-channel device: • VG≤ 0 – no conduction between source and drain • possible because one of the two pn junctions • around source and drain is reverse biased. • 0 < VG< VT – mobile holes repelled from surface below gate. (VT is the Threshold Voltage.) • VG > VT – electrons attracted to surface below gate, surface inverted to become n-type, conduction between source and drain. source n+

MOS FABRICATION n-channel device: • Lightly-doped p-type wafer • Grow thin SiO2 layer for gate insulation • Deposit polycrystalline silicon for gate electrode • Diffuse/implant n-type dopant for source and drain (n+) • Make metal contacts – (gate contact offset)

ENHANCEMENT AND DEPLETION MOSFET’s • Enhancement device – no channel between source and drain for VGS = 0 • Depletion device – channel deliberately created between source and drain during fabrication. • Hence there are 4 MOSFET types: • n-channel enhancement • n-channel depletion • p-channel enhancement • p-channel depletion

ID VDS>VGS-VT VDS=VGS-VT VDS • MOS PINCH-OFF • Channel between source and drain becomes pinched off (i.e. interrupted) when: • VDS≥ VGS – VT