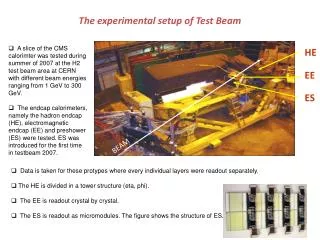

Test-Beam Setup

This document outlines the current status and production timelines for key components in the VFAT Emulator project. It includes details on the various hybrid board transitions to the DOHM system, production status of the RP and GEM hybrids, and the configuration of VFAT emulator boards ready for test-beam setups. Notably, 50 RP hybrids have been ordered with some currently available, alongside specifications for clock generation, trigger management, and data output configurations. The document also discusses I2C interfaces and the latest firmware implementations for effective data handling.

Test-Beam Setup

E N D

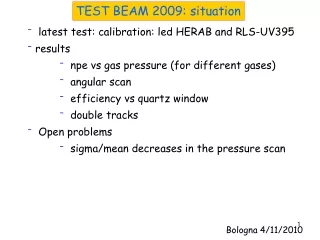

Presentation Transcript

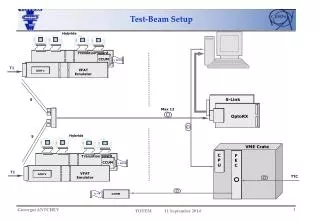

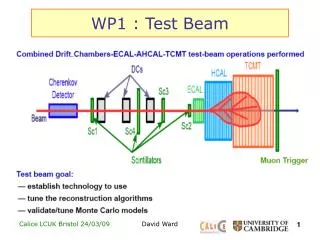

Hybrids FEC CPU T1 S-Link 5 Max 12 OptoRX To DOHM Hybrids 5 Transition Board VME Crate CCUM DOHM CCUM GOH’s GOH’s Transition Board To DOHM T1 TTC VFAT Emulator VFAT Emulator To TB Test-Beam Setup

Test-Beam Boards – Status (1) “Transitions Module”

Test-Beam Boards – Status (2) “RP Hybrid”

Test-Beam Boards – Status (3) “GEM Hybrid” - Production - 50 ordered; - 4 available now; - 20 more –1 week “Transitions Board” - Layout - done; - Production - pending – 1 week “RP Hybrid” - Layout - done; - Production - pending – 2 weeks “VFAT Emulator” - 3 boards available; - 1 full equipped with 12 GOH; - 2 empty

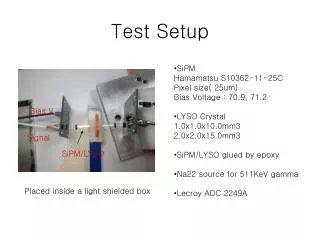

MCLK Altera Cyclone EP1C4F400 QPLL PLL / Clock T1 to VFAT Hybrids GOH Control VFAT Commands ReSynch/CalPulse/LV1A Ext. Trigger Internal Trigger 16 VFAT Data Out Data OUTPUTS Data FIFO 16 X GOH0 16 CAV/DAV/Flags 8 RP Data Out 8 GOH1 16 Trigger OUTPUTS Pattern Generator CAV/DAV/Flags GOH2 16 64 8 x 8 VFAT Triggers Trigger FIFO X CAV/DAV/Flags GOH3 16 32 2 x 16 RP Triggers CAV/DAV/Flags VFAT I2C GOH4 16 VFAT Data Valid 16 Data Valid Synch. 16 CAV/DAV/Flags I2C Test-Beam VFAT Emulator FPGA (1) √ √ √ √ √ √ √

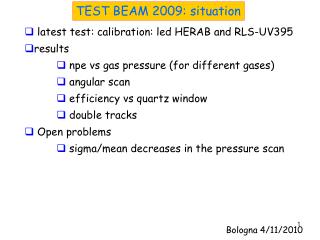

Test-Beam VFAT Emulator FPGA (3) Firmware: - PLL and Clock Generation 40MHz; - T1 Commands; - Internal or External Trigger - DATA Input Buffer (FIFO); - Synch. With DATA Valid - TRIGGER Input Buffer (FIFO); - Use also for Trigger – CC logic - DATA and TRIGGER Output Buffers; - GOH Modules Control; - I2C interface Modes: - Internal Trigger/Commands and Pattern; - External T1 / Data from VFAT Hybrids

0….…………………………..…15 VFAT 0 . . . 192……………………………………………………………………………………………………...…..……………….………..0 176.………………….………..192 . . . . . . . . . 15..………….……..……………..…0 . . . 0….…………………………..…15 VFAT 15 last word first word One Packet 176.………………….………..192 Test-Beam VFAT Emulator FPGA (2) VFAT to GOH Data

Hybrid Hybrid I2C 1,2 To DOHM VFAT VFAT LVDS to CMOS CCUM T1 fan-out CLOCK fan-out LVDS to CMOS Backup Slide (1) …….... Up to 16 Hybrids 8 with + 8 w/o Trigger bits Transition Board Trigger & DATA T1 CLOCK GOH GOH GOH GOH GOH To OptoRX 5 VFAT Emulator T1