第四章 CMOS 电路与逻辑设计

第四章 CMOS 电路与逻辑设计. MOS 晶体管 MOS 的物理结构 CMOS 版图与设计规则 基本 CMOS 逻辑门 基本门版图设计 其他 CMOS 逻辑结构. 4.1 MOS 的物理结构. IC 制造材料 MOS 的物理结构 串联 nMOS 管硅片图形 并联 MOS 管图形. 1. IC 制造材料. 集成电路制造所应用到的材料分类. IC 制造材料 — 硅.

第四章 CMOS 电路与逻辑设计

E N D

Presentation Transcript

第四章 CMOS电路与逻辑设计 • MOS晶体管 • MOS的物理结构 • CMOS版图与设计规则 • 基本CMOS逻辑门 • 基本门版图设计 • 其他CMOS逻辑结构 VLSI

4.1 MOS的物理结构 • IC制造材料 • MOS的物理结构 • 串联nMOS管硅片图形 • 并联MOS管图形 VLSI

1. IC制造材料 集成电路制造所应用到的材料分类 VLSI

IC制造材料—硅 • 硅是集成电路制造的基础材料。硅集成电路是在称为园片(wafer)的较大圆形硅薄片上制造的。Wafer的直径一般100-300mm,厚约0.4-0.7mm。一个规模较大的硅集成电路每边约10mm,所以一个wafer上可以制作许许多多个这样的电路 • 多目标芯片(MPW) • 集成电路制造过程中,wafer从抛光的裸表面开始需要几千个步骤,这一系列步骤中最重要的几个步骤是用来形成cmos结构所需要的材料层及其图案。其余大多数步骤是清洗。aafer是分组进行加工的,一批wafer经过整个工艺线需要几周的时间。 VLSI

IC制造材料 • 二氧化硅:用作mos管的栅氧层,是一种很好的电绝缘材料,能很好的附着在大多数材料上,可以生长或淀积在硅圆片上。 • 金属材料:铝,铬,钛,钼,铊,钨等纯金属和合金薄层在VLSI制造中起着重要作用,纯金属薄层用于制作与工作区的连线,器件间互联线,栅及电容、电感、传输线的电极等。 VLSI

IC制造材料 • 多晶硅:如果在非晶体SiO2层上淀积硅原子,那么硅就会结晶,但却找不到与之对应的可以参照的典型晶体结构。他们形成小的晶体,即为硅晶体的小区域。这样的材料称为多晶硅。 • 多晶硅与单晶硅都是硅原子的集合体且其特性都随结晶度与杂质原子而改变。非掺杂的多晶硅薄层实质上是半绝缘的,电阻率为300 Ω·cm 。通过不同杂质的组合,多晶硅的电阻率可被控制在500—0.005 Ω·cm多晶硅被广泛用于电子工业。在MOS及双极器件中,多晶硅用制作栅极、形成源极与漏极(双极器件的基区与发射区)的欧姆接触、基本连线、薄PN结的扩散源、高值电阻等。 VLSI

2. MOS的物理结构 VLSI

金属层 加上另一层绝缘层和第二层金属层 • 侧视图显示叠放顺序 • 绝缘层将两层金属分隔开,所以他们在电器上不同 • 每层的图形由顶视图表示 VLSI

nFET结构 VLSI

pFET结构 n陷 VLSI

有源区掩模与pSELECT掩模交叉产生p+区 FOX:场氧区 Active:有源区 选择区与有源区 有源区掩模与nSELECT掩模交叉产生n+区 VLSI

金属层与过孔 剖面图 VLSI

有源选择区 金属层1 有源区 有源接触区 金属层1与接触区 金属层1 氧化层1 可以使用多个接触来降低接触电阻 VLSI

金属层1与多晶接触 顶视图 VLSI

3. CMOS中的闩锁(Latch up)现象 Latch up是cmos存在的一种寄生电路效应,它会导致VDD与VSS短路,使芯片烧毁或至少因系统电源关闭而停止工作。产生的原因是VDD与VSS之间产生了pnpn结构。 图(a)所示CMOS反相器,其寄生电路包含了一个NPN型、一个PNP型三极管和电阻Rw、Rs。 Rw是p陷(p衬底)的电阻 Rs是型衬底的电阻 等效电路如图(b)。 VLSI

Latch up T1由P+—N衬—P陷构成,是PNP型三极管;T2由N衬— P陷— P+构成,是NPP型三极管; 如果有足够大的电流流入N型衬底而从P陷流出(即流过Rs), Rs两端的电压将可能足够大使得T1、T2进入线性区而如同一个小电阻,使VDD与VSS之间短路而导致电路故障。 同样的情况也可能发生在Rw上而造成电路故障。 VLSI

Latch up • 减少发生Latch up效应的一般规则: • 每个衬底要有适当的衬底节点(或陷节点) • 每个衬底节点应接到传输电源的金属上 • 衬底节点要尽量靠近所接的电源,以减小Rw和Rs的大小。 • N型器件要靠近VSS,p型器件要靠近VDD。 • 一个N型器件连接到VSS时,其P衬底也要接VSS。一个P型器件连接到VDD时,其N衬底也要接VDD。 最容易发生Latch up的地方是在输入输出焊接区(I/O Pad)结构中,因为那里会有大电流流过。统常I/O Pad由专门人员设计。 VLSI

4. 串联nMOS管硅片图形 串联nMOS管硅片图形 电路图 表面视图 侧视图 VLSI

多晶 n+/p+ 金属 接触 电路图 表面视图 电路图 表面视图 5. 并联MOS管图形 并联MOS管图形 VLSI

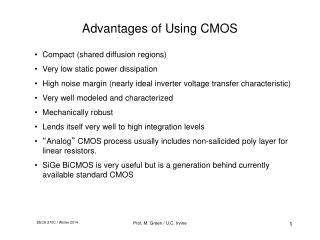

4.2 CMOS版图与设计规则 版图设计的作用是确定一组掩模来定义集成电路。版图设计是运用CAD工具完成的,类似于用一组彩笔在一张格纸上话许多方框。 现代版图设计中,一些电路单元的版图已做好并存在库中。具体设计电路时,可以改变单元的参数来适应需求尺寸,计算机自动生成每层的几何图形。电路有多个单元时,程序会自动排列或连接他们。设计者只需要对自动生成的版图互动地进行修改。 设计者必须直接把握重要单元的版图设计,尤其是当版图要小或电路运行速度要快的情况下。 VLSI

版图与设计规则 版图(Layout)是集成电路设计者将设计并仿真优化后的电路转化成的一系列几何图形,它包含了集成电路尺寸大小、各层拓扑定义等有关器件的所有物理信息。集成电路制造厂家根据这些信息来制造掩膜。版图的设计有特定的规则,这些规则是指导版图掩模设计的对几何尺寸的一组规定。是集成电路制造厂家根据自己的工艺特点而制定的。因此不同的工艺,就有不同的设计规则。设计者只有得到了厂家提供的规则以后,才能开始设计。版图在设计的过程中要进行定期的检查,避免错误的积累而导致难以修改。很多集成电路的设计软件都有设计版图的功能,CadenceDesign System就是其中最突出的一种。Cadence提供称之为Virtuoso的版图设计软件帮助设计者在图形方式下绘制版图。 VLSI

版图与设计规则 • 集成电路的制造必然受到工艺技术水平的限制,受到器件物理参数的制约,为了保证器件正确工作和提高芯片的成品率,要求设计者在版图设计时遵循一定的设计规则,这些设计规则直接由流片厂家提供。设计规则(design rule)是版图设计和工艺之间的接口。 • 设计规则可划分为4种主要类别: • 最小宽度 • 最小间距 • 最小交叠 VLSI

λ设计规则 一组设计规则可能要100页或更多的文件来说明,因此需要相当长的时间去了解。不同的工艺有不同的设计规则。一些工厂如TSMC(台湾半导体制造公司)为许多大的公司和资金充足的客户提供服务以实现他们的设计。由于用户面很广,大多数工厂允客户提交一组比较简单的设计规则的设计,这些规则可以很容易地进行缩放,以适应不同的工艺。这样的设计规则称为λ设计规则。 λ设计规则依据一个参照量λ (单位:微米),所有的宽度、间距等都写成如下形式: 值 = m λ m是比例因子。 VLSI

λ设计规则 • λ设计规则隐含地假设了每个掩模最坏的绝对校准低于0.75λ,这就保证了两个研磨的相对未校准量低于0.15λ。 • 如图所示,λ设计规则规定: 电路中任何两个区 域的最小间距为2λ, 以防止由于重叠引 发破坏性短路。多 晶硅必须延伸到作 用区外至少2λ。 作用区包围接触区 距离至少为1λ。 VLSI

1. 最小宽度(minWidth) 最小宽度指封闭几何图形的内边之间的距离如图所示。在利用DRC(设计规则检查)对版图进行几何规则检查时,对于宽度低于规则中指定的最小宽度的几何图形,计算机将给出错误提示。 VLSI

最小宽度 TSMC_0.35μm CMOS工艺中各版图层的线条最小宽度 对于0.35μm工艺,λ=0.2μm VLSI

2. 最小间距(minSep) 间距指各几何图形外边界之间的距离,如图所示: VLSI

最小间距 TSMC_0.35μm CMOS工艺版图各层图形之间的最小间隔 VLSI

3. 最小交叠(minOverlap) 交迭有两种形式: a)一几何图形内边界到另一图形的内边界长度(overlap),如图(a) b)一几何图形外边界到另一图形的内边界长度(extension),如图(b) VLSI

最小交叠 TSMC_0.35μm CMOS工艺版图各层图形之间最小交叠 VLSI

L n+/p+ W 4.4 单位晶体管设计 单位晶体管:全定制版图设计的起点。单位晶体管是一个具有规定宽长比(W/L)的晶体管,可以按要求在版图上复制。 一种单位晶体管是运用设计规则设计的最小尺寸MOS管,W=Wmin、L=Lmin。如图。 用最小尺寸晶体管理论上可以得到最高的集成度,但不一定是每个电路的最好选择。 VLSI

最小尺寸晶体管 实际的晶体管有源区要与金属层连接,需要增加有源接触。 沟道长度不变,但由于接触孔的存在,沟道的最小宽度为: W=dc+2sa-ac dc:接触的尺寸 sa-ac:在有源区和有源区接触之间的间距 VLSI

L L L L W 2W 单位晶体管的串联 单位晶体管可以进行技术放大 VLSI

单位晶体管的并联 沟道宽度为W异族管子并行连接,构成的管子沟道实际宽度为4W。 VLSI

VDD pullup network out inputs pulldown network VSS 4.4 基本CMOS逻辑门 CMOS逻辑门结构: pMOS nMOS VLSI

1.CMOS反相器(Inverter) VLSI

CMOS与非门(NAND gate) VLSI

CMOS或非门( NOR gate ) VLSI

CMOS复合门(AOI/OAI gates) • AOI = and/or/invert; OAI = or/and/invert. • Implement larger functions. • Pullup and pulldown networks are compact: smaller area, higher speed than NAND/NOR network equivalents. • AOI312: and 3 inputs, and 1 input (dummy), and 2 inputs; or together these terms; then invert. VLSI

circuit symbol invert or and AOI example1 VLSI

AOI example2 VLSI

异或门和异或非门 异或门 异或非门 VLSI

同步RS触发器 VLSI

Pullup/pulldown network design • Pullup and pulldown networks are duals. • To design one gate, first design one network, then compute dual to get other network. • Example: design network which pulls down when output should be 0, then find dual to get pullup network. VLSI

pMOS增强型 nMOS增强型 2. CMOS传输门(TG) 栅源电压VGSn是决定管子截至还是导通的重要参数。 pMOS的特点: 阈值电压VTp小于0,典型值约-0.5~-0.8V。 VGSp <VTp :导通 VGSp >VTp:截至 nMOS的特点: 阈值电压VTn大于0,典型值约0.5~0.7V。 VGSn>VTn:导通 VGSn<VTn:截至 VLSI

VDD Vi(A) 漏 VDD Vi(A) + VGSn - NMOS ON 源 VTn NMOS OFF 0 nMOS增强型的阈值电压 nMOS增强型的阈值电压 VLSI

Vi(A) VDD VDD - VGSp + VGSp-│VTp│ 源 pMOS OFF Vi(A) 漏 pMOS ON 地 0 pMOS增强型的阈值电压 pMOS增强型的阈值电压 VLSI

CMOS传输门(TG) 一个理想的开关允许通过任何输入这个开关的电压,传送逻辑0和逻辑1的情况一样好。 nMOS、pMOS管的导通能力有限,不能使任意范围的电压通过源漏之间。 VLSI

VDD + VTn - VDD + VGSn - out in + Vin=VDD - + Vout=VDD-VTn - out in + Vin=0V - + Vout=0V - nMOS传送一个强的“0” nMOS传送一个强的“0”、一个弱的“1” 传送逻辑0 传送逻辑1 VGSn<VTn:截至 VGSn>VTn:导通 VLSI