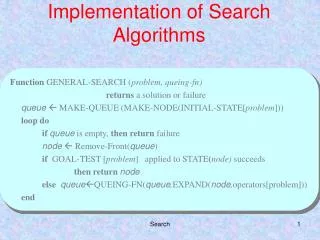

Hardware Implementation of Algorithms Adders

Hardware Implementation of Algorithms Adders. Ernest Jamro, Dep. Of Electronics, AGH, Poland. References. Omondi A.R Computer Arithmetic Systems. Algorithms Architecture and Implementations, Prentice Hall 1994.

Hardware Implementation of Algorithms Adders

E N D

Presentation Transcript

Hardware Implementation of AlgorithmsAdders Ernest Jamro, Dep. Of Electronics, AGH, Poland

References • Omondi A.R Computer Arithmetic Systems. Algorithms Architecture and Implementations, Prentice Hall 1994. • Pirsch P., Architectures for Digital Signal Processing, Chichester UK, Wiley 1998. • U.Mayer-Baese Digital Signal Processing with Field Programmable Gate Arrays, Springer, Berlin 2001 • Keshab K. Parhi VLSI Digital Signal Processing Systems, J.Wiley & sons, 1999 • Kazimierz Wiatr Akceleracja Obliczeń w systemach wizyjnych, WNT, W-wa 2003 • E. Jamro, K. Wiatr, Układy mnożące przez stały współczynnik implementowane w układach programowalnych FPGA, http://home.agh.edu.pl/~jamro/2001KCM_pl.pdf • www.xilinx.com • www.altera.com

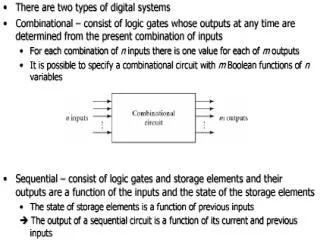

ci-1\ai,bi ci-1\ai,bi 00 00 01 01 11 11 10 10 0 0 0 0 0 1 1 0 0 1 1 1 0 1 1 0 1 1 1 0 Układ dodający ze szeregową propagacją przeniesienia Ripple Carry Adder ai + bi+ci-1 = si + 2·ci si = ai bi ci-1 ci= ai bi + ai ci-1 + bi ci-1= ai bi + ci-1 (ai bi) si ci

ci-1\ai,bi ci-1\ai,bi 00 00 01 01 11 11 10 10 0 0 0 0 1 1 0 0 0 1 1 1 1 1 1 0 1 1 0 0 Odejmowanie / Subtraction (A-B) Odejmowanie bezpośrednie Direct Subtruction Kod uzupełnień do dwóch U2 Two’s Complement ai - bi-ci-1 = si - 2·ci si = ai bi ci-1 Add 1 to LSB negacja każdego bitu Invert each bit bit znaku sign bit si Zamiast odejmowania należy dokonać konwersji do kodu U2 liczby b oraz przeprowadzić zwykłą operację dodawania a+b’ Instead of performing a direct subtraction; a standard adder can be employed but B must be converted to 2’s complement code ci na czerwono różnica pomiędzy dodawaniem Red – difference between addition and subtruction

Ripple Carry Adders in FPGAs si= ai bi ci-1 Fragment of Virtex Configurable Logic Block (CLB)

Carry Skip Adder (CSA)(sumator z przeskokiem przeniesień) Tn= An + Bn (lub / or) Tn= An xor Bn

Carry Skip Adder Szybkość (propagation time - T) Koszt (Area – A) AT= 1/Wydajność (efficiency) m- wielkość bitowa pojedynczego bloku (width of a block)

Układ / Architecture Układ /Architecture Opóźnienie Propagation delay Opóźnienie Koszt Koszt Area (AT)[104] (AT) [104] Carry Look Ahead Carry Look Ahead 4 4 50624 7392 2.94 20.25 Ripple CLA (m=4) Ripple CLA (m=4) 10 34 1334 336 4.57 0.34 carry select (m=4) carry select (m=4) 6 6 992 2688 1.61 0.6 carry skip carry skip 15 29 960 240 2.50 0.36 2-level carry skip 2-level carry skip 12 28 1140 300 0.36 3.19 Ripple Carry Ripple Carry 31 127 224 896 11.38 0.69 Porównanie układów dodających o szerokości Comparison of Different Adders Architectures16 bit 64 bity

Dodawanie 3-wejściowe z propagacją przeniesienia3+ input Carry Propagate Adder (CPA) S= A + B + C CPA – układ dodający np. ze skrośną propagacją przeniesienia (Ripple Carry), Carry Look Ahead, Carry Select Adder Example of Ripple Carry Adder

Dodawanie 3-wejściowe / Addition 3 InputsZachowywanie przeniesienia. Carry Save Adder (CSA) A+B+C= 2 ·T + S ai + bi+ci = 2·ti+1 + si si = ai bi ci ti+1= ai bi + ai ci + bi ci= ai bi + ci (ai bi) Nie ma propagacji przeniesienia Bardzo szybki układ dodający przy powierzchni podobnej jak Ripple-Carry Adder

CSA – 3+ inputs 3-inputs 4-inputs 6-inputs In FPGA dedicated carry logic is available therefore CSA is not so popular as in ASIC technology

Carry Lookahead Adder Si = Ai Bi Ci-1 Ci= Ai Bi + Ai Ci-1 + Bi Ci-1= Ai Bi + Ci-1 (Ai Bi) Gi= Ai Bi – Generate - Propagate Pi= AiBi - Propagate bo: - Generate Si= Pi Ci-1 Ci= Gi + Pi Ci-1 S0= P0 C-1 C0= G0 + P0 C-1 S1= P1 C0 C1= G1 + P1 C0= G1 + P1(G0 + P0 C-1)= G1 + P1G0 + P1P0C-1 S2 = P2 C1 C2= G2 + P2 C1= G2 + P2G1 + P2P1G0 + P2P1P0C-1

RCLA koszt i szybkość Koszt A Czas prop. T AT= 1/Wydajność