Memory

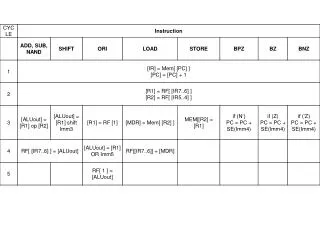

8. 8. ALU1. R1Sel. ALUop. IRload. RFWrite. 0. 3. 8. IR6-7. 0. 8. 2. 8. data1. R1. 1. reg1. 2. AddrSel. 1. 1. MemRead. MemWrite. ALUout. ALU2. 2. ALU. IR5-4. RF. reg2. 8. IR. 8. 0. 8. data2. R2. 000. ADDR. PC. 8. 1. 8. 8. regw. dataw. 8. 1. 001.

Memory

E N D

Presentation Transcript

8 8 ALU1 R1Sel ALUop IRload RFWrite 0 3 8 IR6-7 0 8 2 8 data1 R1 1 reg1 2 AddrSel 1 1 MemRead MemWrite ALUout ALU2 2 ALU IR5-4 RF reg2 8 IR 8 0 8 data2 R2 000 ADDR PC 8 1 8 8 regw dataw 8 1 001 Memory 8 4 8 Imm4 SE 010 8 FlagWrite N Z Data_in Data_out 5 8 Imm5 PCwrite ZE 011 MDR Imm3 ZE 100 RegIn MDRload

ADD R1 R2 • Read mem[PC] • Decode • Read R1, Read R2 • R1 = inst 7,6 • R2 = inst 5,4 • tmp = R1 + R2 • R1 = tmp • set Z, N • PC = PC + 1

CYCLE 1: IR = Mem[PC] 8 8 ALU1 R1Sel ALUop IRload RFWrite 0 3 8 IR6-7 0 8 2 8 data1 R1 1 reg1 2 AddrSel 1 1 MemRead MemWrite ALUout ALU2 2 ALU IR5-4 RF reg2 8 IR 8 0 8 data2 R2 000 ADDR PC 8 1 8 8 regw dataw 8 1 001 Memory 8 4 8 Imm4 SE 010 8 FlagWrite N Z Data_in Data_out 5 8 Imm5 PCwrite ZE 011 MDR Imm3 ZE 100 RegIn MDRload

CYCLE 2: Decode 8 8 ALU1 R1Sel ALUop IRload RFWrite 0 3 8 IR6-7 0 8 2 8 data1 R1 1 reg1 2 AddrSel 1 1 MemRead MemWrite ALUout ALU2 2 ALU IR5-4 RF reg2 8 IR 8 0 8 data2 R2 000 ADDR PC 8 1 8 8 regw dataw 8 1 001 Memory 8 4 8 Imm4 SE 010 8 FlagWrite N Z Data_in Data_out 5 8 Imm5 PCwrite ZE 011 MDR Imm3 ZE 100 RegIn MDRload

CYCLE 3: R1 = RF[IR7,6] & R2 = RF[IR5,4] 8 8 ALU1 R1Sel ALUop IRload RFWrite 0 3 8 IR6-7 0 8 2 8 data1 R1 1 reg1 2 AddrSel 1 1 MemRead MemWrite ALUout ALU2 2 ALU IR5-4 RF reg2 8 IR 8 0 8 data2 R2 000 ADDR PC 8 1 8 8 regw dataw 8 1 001 Memory 8 4 8 Imm4 SE 010 8 FlagWrite N Z Data_in Data_out 5 8 Imm5 PCwrite ZE 011 MDR Imm3 ZE 100 RegIn MDRload

CYCLE 4: AluOut = R1 + R2, Update Z & N 8 8 ALU1 R1Sel ALUop IRload RFWrite 0 3 8 IR6-7 0 8 2 8 data1 R1 1 reg1 2 AddrSel 1 1 MemRead MemWrite ALUout ALU2 2 ALU IR5-4 RF reg2 8 IR 8 0 8 data2 R2 000 ADDR PC 8 1 8 8 regw dataw 8 1 001 Memory 8 4 8 Imm4 SE 010 8 FlagWrite N Z Data_in Data_out 5 8 Imm5 PCwrite ZE 011 MDR Imm3 ZE 100 RegIn MDRload

CYCLE 5: RF[IR7,6] = AluOut 8 8 ALU1 R1Sel ALUop IRload RFWrite 0 3 8 IR6-7 0 8 2 8 data1 R1 1 reg1 2 AddrSel 1 1 MemRead MemWrite ALUout ALU2 2 ALU IR5-4 RF reg2 8 IR 8 0 8 data2 R2 000 ADDR PC 8 1 8 8 regw dataw 8 1 001 Memory 8 4 8 Imm4 SE 010 8 FlagWrite N Z Data_in Data_out 5 8 Imm5 PCwrite ZE 011 MDR Imm3 ZE 100 RegIn MDRload

CYCLE 6: PC = PC + 1 8 8 ALU1 R1Sel ALUop IRload RFWrite 0 3 8 IR6-7 0 8 2 8 data1 R1 1 reg1 2 AddrSel 1 1 MemRead MemWrite ALUout ALU2 2 ALU IR5-4 RF reg2 8 IR 8 0 8 data2 R2 000 ADDR PC 8 1 8 8 regw dataw 8 1 001 Memory 8 4 8 Imm4 SE 010 8 FlagWrite N Z Data_in Data_out 5 8 Imm5 PCwrite ZE 011 MDR Imm3 ZE 100 RegIn MDRload

CYCLE 1: IR = Mem[PC] CYCLE 2: Decode CYCLE 3: R1 = RF[IR7,6] & R2 = RF[IR5,4] CYCLE 4: AluOut = R1 + R2, Update Z & N CYCLE 5: RF[IR7,6] = AluOut CYCLE 6: PC = PC + 1

8 8 ALU1 R1Sel ALUop IRload RFWrite 0 3 8 IR6-7 0 8 2 8 data1 R1 1 reg1 2 AddrSel 1 1 MemRead MemWrite ALUout ALU2 2 ALU IR5-4 RF reg2 8 IR 8 0 8 data2 R2 000 ADDR PC 8 1 8 8 regw dataw 8 1 001 Memory 8 4 8 Imm4 SE 010 8 FlagWrite N Z Data_in Data_out 5 8 Imm5 PCwrite ZE 011 MDR Imm3 ZE 100 RegIn MDRload

SUB R1 R2 • Read mem[PC] • Decode • Read R1, Read R2 • R1 = inst 7,6 • R2 = inst 5,4 • tmp = R1-R2 • R1 = tmp • set Z, N • PC = PC + 1

8 8 ALU1 R1Sel ALUop IRload RFWrite 0 3 8 IR6-7 0 8 2 8 data1 R1 1 reg1 2 AddrSel 1 1 MemRead MemWrite ALUout ALU2 2 ALU IR5-4 RF reg2 8 IR 8 0 8 data2 R2 000 ADDR PC 8 1 8 8 regw dataw 8 1 001 Memory 8 4 8 Imm4 SE 010 8 FlagWrite N Z Data_in Data_out 5 8 Imm5 PCwrite ZE 011 MDR Imm3 ZE 100 RegIn MDRload

NAND R1 R2 • Read mem[PC] • Decode • Read R1, Read R2 • R1 = inst 7,6 • R2 = inst 5,4 • tmp = R1 nand R2 • R1 = tmp • set Z, N • PC = PC + 1

8 8 ALU1 R1Sel ALUop IRload RFWrite 0 3 8 IR6-7 0 8 2 8 data1 R1 1 reg1 2 AddrSel 1 1 MemRead MemWrite ALUout ALU2 2 ALU IR5-4 RF reg2 8 IR 8 0 8 data2 R2 000 ADDR PC 8 1 8 8 regw dataw 8 1 001 Memory 8 4 8 Imm4 SE 010 8 FlagWrite N Z Data_in Data_out 5 8 Imm5 PCwrite ZE 011 MDR Imm3 ZE 100 RegIn MDRload

ORI imm5 • Read mem[PC] • Decode • Read K1 • tmp = K1 or ZE(Imm5) • Imm5 = Inst7,3 • K1 = tmp • set Z, N • PC = PC + 1

8 8 ALU1 R1Sel ALUop IRload RFWrite 0 3 8 IR6-7 0 8 2 8 data1 R1 1 reg1 2 AddrSel 1 1 MemRead MemWrite ALUout ALU2 2 ALU IR5-4 RF reg2 8 IR 8 0 8 data2 R2 000 ADDR PC 8 1 8 8 regw dataw 8 1 001 Memory 8 4 8 Imm4 SE 010 8 FlagWrite N Z Data_in Data_out 5 8 Imm5 PCwrite ZE 011 MDR Imm3 ZE 100 RegIn MDRload

LOAD R1 (R2) • Read mem[PC] • Decode • Read R2 • tmp = Mem(R2) • R1 = tmp • PC = PC + 1

8 8 ALU1 R1Sel ALUop IRload RFWrite 0 3 8 IR6-7 0 8 2 8 data1 R1 1 reg1 2 AddrSel 1 1 MemRead MemWrite ALUout ALU2 2 ALU IR5-4 RF reg2 8 IR 8 0 8 data2 R2 000 ADDR PC 8 1 8 8 regw dataw 8 1 001 Memory 8 4 8 Imm4 SE 010 8 FlagWrite N Z Data_in Data_out 5 8 Imm5 PCwrite ZE 011 MDR Imm3 ZE 100 RegIn MDRload

Store R1 (R2) • Read mem[PC] • Decode • Read R2, R1 • Mem(R2) = R1 • PC = PC + 1

8 8 ALU1 R1Sel ALUop IRload RFWrite 0 3 8 IR6-7 0 8 2 8 data1 R1 1 reg1 2 AddrSel 1 1 MemRead MemWrite ALUout ALU2 2 ALU IR5-4 RF reg2 8 IR 8 0 8 data2 R2 000 ADDR PC 8 1 8 8 regw dataw 8 1 001 Memory 8 4 8 Imm4 SE 010 8 FlagWrite N Z Data_in Data_out 5 8 Imm5 PCwrite ZE 011 MDR Imm3 ZE 100 RegIn MDRload

BZ Imm4 • Read mem[PC] • Decode • if (Z is true) PC = PC + 1 + SE (Imm4) • else PC = PC + 1

8 8 ALU1 R1Sel ALUop IRload RFWrite 0 3 8 IR6-7 0 8 2 8 data1 R1 1 reg1 2 AddrSel 1 1 MemRead MemWrite ALUout ALU2 2 ALU IR5-4 RF reg2 8 IR 8 0 8 data2 R2 000 ADDR PC 8 1 8 8 regw dataw 8 1 001 Memory 8 4 8 Imm4 SE 010 8 FlagWrite N Z Data_in Data_out 5 8 Imm5 PCwrite ZE 011 MDR Imm3 ZE 100 RegIn MDRload

PCSel 0 8 1 R1Sel RFWrite ALUop Inst7-6 8 0 3 2 8 data1 reg1 2 1 1 1 ALU2 Inst5-4 2 RF reg2 8 ALU 8 data2 00 ADDR PC 8 8 regw dataw 8 8 IM Inst7-3 8 5 Imm5 ZE 01 8 FlagWrite N Z Inst5-3 Imm3 INST ZE 10 PCwrite Imm4 4 SE 11 8 Inst7-4 RegIn 0 1 8 8 MemRead MemWrite 8 1 8 ADDR 8 Data Memory 8 8 Data_in Data_out 8