Evaluating FPGA-Based Hypercomputers for NASA's Advanced Scientific Computations

This report explores the potential of FPGA-based hypercomputers to enhance scientific computations for NASA. Led by Drs. Olaf Storaasli and Robert Singleterry, the team investigates the efficiency and speed of novel FPGA architectures compared to traditional CPUs. With projects leveraging advanced gateware like VIVA, the research focuses on matrix algebra, dynamic analysis, and probabilistic computations. Results indicate significant performance improvements from initial GFLOPS to future projections of up to 470 GFLOPS, highlighting FPGAs' promise for complex NASA engineering applications.

Evaluating FPGA-Based Hypercomputers for NASA's Advanced Scientific Computations

E N D

Presentation Transcript

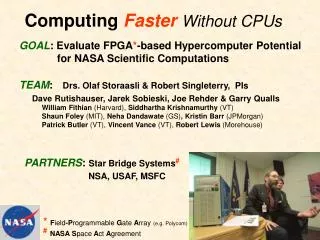

ComputingFasterWithoutCPUs GOAL: Evaluate FPGA*-based Hypercomputer Potential for NASA Scientific Computations TEAM: Drs. Olaf Storaasli & Robert Singleterry, PIs Dave Rutishauser, Jarek Sobieski, Joe Rehder & Garry Qualls William Fithian (Harvard), Siddhartha Krishnamurthy (VT) Shaun Foley (MIT), Neha Dandawate (GS), Kristin Barr (JPMorgan) Patrick Butler (VT), Vincent Vance (VT), Robert Lewis (Morehouse) PARTNERS: Star Bridge Systems# NSA, USAF, MSFC *Field-Programmable Gate Array (e.g. Polycom) #NASA Space Act Agreement

William Fithian*(Harvard, Merit Scholar, Oracle Award) *NASA-NHGS mentorship ‘00-’02

FPGA: New Computing Paradigm Traditional CPU Reconfigurable FPGA Sequential: 1 operation/cycle Parallel: Inherent Fixed gates & data types Dynamic gates & data types Wasteful: 99% gates idle/cycle yet all draw power Efficient: Optimizes gates to task Software: Text Gateware: VIVA Icons & Transports do i = 1, billion c= a+b end do 392+ MFLOPS/64 MHz FPGA 3.92+ GFLOPS/10 FPGA board 26 MFLOPS/250 MHz SGI

VIVA 1 (Feb ’01)VIVA2 (July ’02) VIVA: Gateware Development Tool What: Simple tool to configure FPGAs (VHDL cumbersome) How: Transforms high-level graphical code to logic circuitry Why: Achieve near-ASIC speed(w/o chip design) Growth in VIVA Capability Extensive Data Types Trig, Logs, Transcendentals File Input/Output Vector-Matrix Support Access to Multiple FPGAs Extensive Documentation Stable Development Few “bugs” NO Floating Point NO Scientific Functions NO File Input/Output NO Vector-Matrix Support Access to One FPGA Primitive Documentation Weekly Changes Frequent “bugs”

Langley Hypercomputers 10 FPGAs each

Langley Algorithms Developed* • Matrix Algebra: Vectors, Matrices, Dot Product • Factorial=> Probability: Combinations/Permutations AIRSC • Cordic=> Transcendentals: sin, log, exp, cosh… • Integration & Differentiation(numeric) • Matrix Equation Solver: [A]{x} = {b} via Gauss & Jacobi . • Dynamic Analysis: [M]{ü} + [C]{u} + [K]{u} + NLT = {P(t)} • Analog Computing: digital implementation • Nonlinear Analysis: “Analog” simulation avoids NLT solution development time *InAIAA& Military & Aerospace Programmable Logic Device (MAPLD) papers

f(x) x Dx Numeric Integration Output (Area under curve) S f(x)*Dx xi+1=xi+Dx Dx f(x)=x2 f(x)*Dx Control

VIVA Sparse Matrix Equation SolverJacobi Iterative (3x3 Demo) [A]{x}={b} x1 = 1/A11*(b1 - A12*x2 - A13*x3) Control 3 Row Loads 3 // Dot Products

HAL15 HAL15 HAL30 HC-62M120x power HAL15LaRC West Robert @ SBS DARPA Prop. with NSA NSA NSAx2 NASA-SBS SAA SBS SBS SBS NASA-SBS SAA Aug ‘01 Dec ‘01 May ‘02 Aug ‘02 Year 2 Progress - Roadmap Hardware VIVA1 VIVA1.5 VIVA2 VIVA Pathfinder NASA Engineering Analog Computing Large-scale Struc. Anal. Weather Code NL Structural Analysis ¦f(x)dx Dynamic Anal. [A]{x}={b} 106 eq.s Cordic dy/dx Apps JPL N! Partners USAF OSC PF MAPLD Conf.

Xilinx FPGA Gates Multiplies in H/W Clock Speed MHz Memory Memory Speed Reconfigure Time GFLOPS Total GFLOPs XC4062 62K 0 100 20Kb 466 Gb/s 100ms 0.4 4 (10 FPGAs) XC2V6000 6 million (97x) 144 (18x18) 300 (3x) 3.5 Mb (175x) 5 Tb/s (11x) 40ms (2.5x) 47 (120x) 470 (10 FPGAs) Year 2: Exploit Latest FPGAs Rapid Growth in FPGA Capability FPGA (Feb ’01) FPGA (Aug ’02) Plans: -Millions of Matrix Equations for Structures, Electromagnetics & Acoustics -Rapid Static & Dynamic Structural Analyses -Cray Vector Computations in Weather Code (VT PhD) - Robert on Administrator’s Fellowship at Star Bridge Systems - Joint proposals with NSA & DARPA - Simulate advanced computing concepts using VIVA - Collaborate with SBS to expand VIVA libraries - Influence VIVA development to meet NASA application needs - Expand FPGA applications for NASA programs

SummaryWhat We’ve Learned We like FPGA promise – accomplished much Hardware: Tested 2 futuristic FPGA systems FPGAs: Inherently //, flexible, efficient, & fast VIVA: Powerful & growing (tailored to NASA needs) Applications: Diverse “pathfinder” algorithms developed FPGA technology: Advancing dramatically Speed: Year 1: 4 GFLOPS => Year 2: 470 GFLOPS Future: Year 2 promises “cutting edge” innovations comprehensive NASA engineering applications