Computing Faster without CPUs

This project evaluates the potential of FPGA-based Hypercomputers for NASA scientific computations. The team, led by Dr. Olaf Storaasli, collaborates with various partners and uses innovative FPGA programming techniques to achieve efficient computing without traditional CPUs. The project utilizes tools like VIVA for custom chip design gateware and develops complex algorithms for matrix algebra, dynamic analysis, and more. With a focus on parallelism and efficient gate optimization, the project aims to enhance computing speeds and capabilities for NASA applications.

Computing Faster without CPUs

E N D

Presentation Transcript

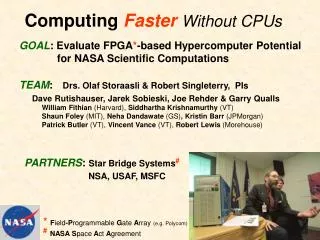

Computing Faster without CPUs Scientific Applications on FPGA-based* Reconfigurable Hypercomputers by Dr. Olaf Storaasli Analytical & Computational Methods Branch Structures and Materials for May Seminar, Electronic Systems Branch *Field-Programmable Gate Array

NASA Research Background FEA: NASTRAN Viking ==> Mars IPAD: Integrated Design NASA Fellowship: Norway Finite Element Machine: Early // Computer Cray GigaFLOP Award: Shuttle SRB Matrix Equation Solver: FORTRAN, C, Java Lanczos Eigensolver: 88x Speedup Intel: Supercomputer Users Board, P6 Award Symposia: Large-Scale Apps. (5) NASA Software of the Year Award Creativity & Innovation Awards 2

Exploring ScientificApplicationson Reconfigurable Hypercomputers 62K gates/FPGA 6M gates/FPGA Creativity & Innovation ‘02 ‘03 3

ComputingFasterWithoutCPUs GOAL: Evaluate FPGA*-based Hypercomputer Potential for NASA Scientific Computations TEAM:Dr. Olaf Storaasli, Principal Investigator Jarek Sobieski, Robert Singleterry, Dave Rutishauser, Joe Rehder Garry Qualls , William Fithian-Harvard, Siddhartha Krishnamurthy-VT Shaun Foley-MIT, Cris Kania-GS, Neha Dandawate-GS, Patrick Butler-VT Kristin Barr-JPMorgan, Robert Lewis-Morehouse , Vincent Vance-VT PARTNERS: Star Bridge Systems, NSA, USAF, MSFC 4

William Fithian*(Harvard, Merit Scholar, Oracle Award) *NASA-NHGS mentorship ‘00-’02 5

First Langley Hypercomputers 10 FPGAs each 6

FPGA Programming • User controls gates: middle man removed • Code options: • 1-D Text, sequential FORTRAN-like: C-to-Gate, VHDL • parallelism esoteric • 3-D Graphic, paralleldrag & drop: Viva • Parallelism inherent • data flow like analog computer NASA Hypercomputers 8

FPGA: New Computing Paradigm Traditional CPU Reconfigurable FPGA Sequential: 1 operation/cycle Parallel: Inherent Fixed gates & data types Dynamic gates & data types Wasteful: 99% gates idle/cycle yet all draw power Efficient: Optimizes gates to task Software: Text - 1D Gateware: VIVA Icons & Transports do i = 1, billion c= a+b end do 392+ MFLOPS/64 MHz FPGA 3.92+ GFLOPS/10 FPGA board 26 MFLOPS/250 MHz SGI 9

Select-Drag-Drop to Code “icon” Primitives Add new code to library Complex algorithms “drill in” 10

VIVA 1 (Feb ’01)VIVA2 (July ’02) VIVA:Custom Chip Design Gateware What: Graphics tool to “route” FPGAs (VHDL cumbersome) How: Converts icon-transport “gateware” to circuit logic Why: Achieve near-ASIC speed(w/o chip design $) Growth in VIVA Capability Extensive Data Types Trig, Logs, Transcendentals File Input/Output Vector-Matrix Support Access to Multiple FPGAs Extensive Documentation Stable Development Few “bugs” NO Floating Point NO Scientific Functions NO File Input/Output NO Vector-Matrix Support Access to One FPGA Primitive Documentation Weekly Changes Frequent “bugs” 11

Viva User1 Viva User2 Viva User3 Viva User4 Viva User5 Viva User6 Parallel Use of Parallel FPGAs Windows Server Control Panel HC-38m Hypercomputer 7 FPGAs 6M Gates 13

Algorithms Developed* • Matrix Algebra: {V}, [M], {V}T{V}, [M]x[M],GCD,… • n!=> Probability: Combinations/Permutations AirSC • Cordic=> Transcendentals: sin, log, exp, cosh… • ∂y/∂x& ∫f(x)dx=> Runge-Kutta: CFD, Newmark Beta: CSM • Matrix Equation Solver: [A]{x} = {b} - Gauss & Jacobi . • Dynamic Analysis: [M]{ü} + [C]{u} + [K]{u} + NLT = {P(t)} • Analog Computing: digital accuracy • Nonlinear Analysis: Analog simulation • avoids NLT devp’t time *InAIAA& Military & Aerospace Programmable Logic Device (MAPLD) papers 14

f(x) x Dx Numeric Integration Output (Area under curve) S f(x)*Dx xi+1=xi+Dx Dx f(x)=x2 f(x)*Dx Control 15

VIVA Sparse Matrix Equation SolverJacobi Iterative (3x3 Demo) [A]{x}={b} x1 = 1/A11*(b1 - A12*x2 - A13*x3) Control 3 Row Loads 3 // Dot Products 16

Analog Diagram of 2x2 Equations Solution bz bz z P-bz x b - input P yi = (P - b zi-1)/a / y a - initialized output y y x d - M zi = (M - dyi-1)/e input / z e output z 17

Xilinx FPGA Gates Multiplies on chip Clock Speed MHz Memory on chip Memory Speed Reconfigure Time GFLOPS Total GFLOPs XC4062 62K 0 100 20Kb 466 Gb/s 100ms 0.4 4 (10 FPGAs) XC2V6000 6 million (97x) 144 300 (3x) 3.5 Mb (175x) 5 Tb/s (11x) 40ms (2.5x) 47 (120x) 329 (7 FPGAs) Year 2: Exploit Latest FPGAs Rapid Growth in FPGA Capability FPGA (Feb ’01) FPGA (Oct ’02) Plans: -Millions of Matrix Equations: Structures, Electromagnetics & Acoustics -Rapid Static & Dynamic Structural Analyses -Cray Vector Computations in Weather Code (VT PhD) - Robert on Administrator’s Fellowship at Star Bridge Systems - Simulate advanced computing concepts using VIVA - Collaborate with SBS, NSA, A&T… to expand VIVA libraries - Tailor VIVA development for NASA applications - Target applications to NASA programs (e.g. EDB Collaboration??) 19

SummaryWhat We’re Learning We like FPGA promise – accomplished much Hardware: Testing 3 futuristic FPGA systems FPGAs: Inherently //, flexible, efficient, & fast, dramatic advances VIVA: Powerful & growing (tailor to NASA needs) Applications: ‘02 - Diverse “pathfinder” algorithms developed ‘03 - Comprehensive NASA engineering applications Speed: Year 1: 4 GFLOPS => Year 2: 329 GFLOPS Future: exploit capability on NASA “cutting edge” innovations 20

Langley Reconfigurable Computing Research 1. Singleterry, Robert C., Jaroslav Sobieszczanski-Sobieski, and Samuel Brown. “Field-Programmable Gate Array Computer in Structural Analysis: an Initial Exploration.” 43rd American Institute of Aeronautics and Astronautics (AIAA) Structures, Structural Dynamics, and Materials Conference.April 22-25, 2002. 2. Storaasli, Olaf O., Robert C. Singleterry, and Samuel Brown. “Scientific Computations on a NASA Reconfigurable Hypercomputer.” Abstract accepted for 5th Military and Aerospace Programmable Logic Devices (MAPLD) Conference, Paper in preparation. September 10-12, 2002. 3. Fithian, William, Samuel Brown, and Tyler Reed. “Object Synchronization in VIVA 1.5.” Briefing prepared for VIVA users at NASA Marshall, Eglin AFB, Progress Forge, Inc., and Star Bridge Systems, Inc.March 26, 2002. 4. Barr, Kristen, Shaun Foley, and Robert A. Lewis II. “Hypercomputing with the CORDIC Algorithm.” August, 2001. Presentation of research conducted under Dr. Olaf O. Storaasli, June-August, 2001. 5. Butler, Patrick. New Horizons Governors School Mentorship Project. May, 2001. Presentation of research conducted under Dr. Olaf O. Storaasli, September 2000 – May 2001. 6. Dandawate, Neha. “Reckless Speeding: The Investigation of the Programming Capabilities of the HAL Hypercomputer.” July, 2002. Presentation of research conducted under Dr. Olaf O. Storaasli, June – July, 2002. 7. Dandawate, Neha. “The Investigation of the Programming Capabilities of the HAL-15 Hypercomputer.” July, 2002. Paper on research conducted under Dr. Olaf O. Storaasli, June – July, 2002. 8. Fithian, William. “Developing a Matrix Equation Solver for the HAL-15 Hypercomputer.” December, 2001. Proposal for research to be conducted under Dr. Olaf O. Storaasli, September 2001 – May 2002. 9. Fithian, William. “Developing a Matrix Equation Solver for the HAL-15.” May, 2002. Presentation of research conducted under Dr. Olaf O. Storaasli, September 2001 – May 2002. 10. Fithian, William. “Jacobi Iterative Matrix Equation Solver for Star Bridge Systems FPGA Hypercomputer.” September, 2002. In preparation. 11. Foley, Shaun. “Scientific Hypercomputing.” August, 2001. Paper describing research conducted under Dr. Olaf O. Storaasli, June – August, 2001. 12. Krishnamurthy, Siddhartha. “Development of an Integration Algorithm for Field Programable Gate Arrays using VIVA.” July, 2002. Paper describing research conducted under Dr. Robert C. Singleterry, June – Aug 2002. Further Information: Google: “olaf acmb” 21