CLOCK DISTRIBUTION

CLOCK DISTRIBUTION. Shobha Vasudevan. The clock distribution problem. Large Chip Area Different flop densities Non-uniform distribution of flops All flops need to get clock signal at the same time Power budget Clock routing:hard problem. Stages of Clock design.

CLOCK DISTRIBUTION

E N D

Presentation Transcript

CLOCK DISTRIBUTION Shobha Vasudevan

The clock distribution problem • Large Chip Area • Different flop densities • Non-uniform distribution of flops • All flops need to get clock signal at the same time • Power budget • Clock routing:hard problem

Stages of Clock design • Global Routing (matched impedance) • Impedance matching at every block • Local Routing within every block

Iterations of the clock tree • First iteration on floorplan

Assumptions made in initial iterations • Flop Distribution not decided • LCB placement and distribution not decided • LCBs placed at the entry point of “H” in block • Matched Impedance at every entry point of global tree in block

Third Iteration: Impedance Matching Assumptions: LCBs placed on edge of blocks Internal Routing of clock from LCBs to blocks Uniform distribution of flops in random logic blocks (Control, System and Exceptions)

Directives in clock tree design • Zero or minimal skew to LCBs • Skew budget: 20 ps • No routing over arrays (Caches and MMUs) • Extensive wiring over Control block • Routing through the center for uniformly distributed flop regions.

Directives in clock tree design • M5 for horizontal lines • M6 for vertical lines • Gated flops in the LSU, MAC and GPR region

Clock Tree Design:Binary Tree • Uniform distribution of load • Division into clusters of 8-9 LCBs • Binary tree with each cluster as a leaf node • “Levels” of binary tree as equivalent capacitance points • Unbalanced branches of tree balanced by adding equivalent capacitance • Balancing capacitance:Extra wire routing

Routing issues • GCBs placed at root and ends of pink and blue lines (16+4+1) • Equivalent capacitances maintained at every level of the tree • Wire length and thickness varied to match capacitance

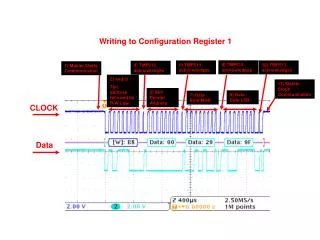

Hspice simulation • Capacitance and resistance of M5 and M6 factored for every horizontal and vertical branch • Balancing capacitance added • Skew found for all 47 leaf nodes

Skew introducing factors • Different capacitances at the leaf nodes (8 LCBs or 9 LCBs) • M5 and M6 not accounted for in the routing • Discrepancies in length of wire

The BST-DME algorithm • Academic tool (Andrew Kahn, UCLA) • Uses Divide-Merge-Embed Algorithm • Calculates minimum wire length for bounded skew • Accepts coordinates of LCBs and their capacitances • Baseline Metric

To be done • Precharge of Caches not routed • Plan: • Add capacitive load of precharge LCBs to the corresponding leaf nodes • Route extra wire for the other branches to balance load • Timeline: May 1st