Pulse-Width Modulated DAC

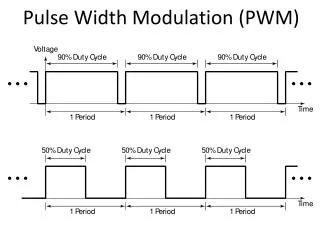

Pulse-Width Modulated DAC. Lecture 11.3 Verilog Section 11.5. 8-Bit Counter. Pulse-Width Modulation. module counter8 ( Q ,clr ,clk ); input clr ; wire clr ; input clk ; wire clk ; output [7:0] Q ; reg [7:0] Q ; // 8-bit counter always @( posedge clk or posedge clr)

Pulse-Width Modulated DAC

E N D

Presentation Transcript

Pulse-Width Modulated DAC Lecture 11.3 Verilog Section 11.5

module counter8 ( Q ,clr ,clk ); input clr ; wire clr ; input clk ; wire clk ; output [7:0] Q ; reg [7:0] Q ; // 8-bit counter always @(posedge clk orposedge clr) begin if(clr == 1) Q <= 0; else Q <= Q + 1; end endmodule

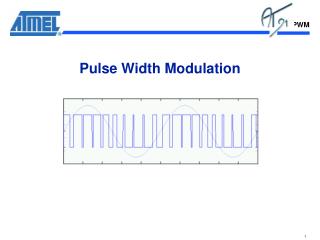

module PWM(clk,clr,duty,pwm); input clk, clr; input [7:0] duty; output pwm; reg pwm; wire [7:0] count; wire set, reset; assign set = &count; assign reset = (count == duty); always @(posedge set orposedge reset orposedge clr) begin if(clr == 1) pwm <= 0; else begin if(set == 1) pwm <= 1; if(reset == 1) pwm <= 0; end end counter8 CNT(.Q(count),.clr(clr),.clk(clk));