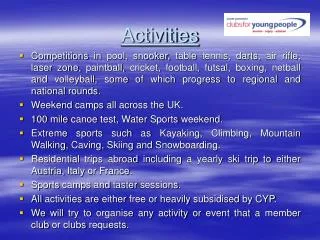

Activities

MICROELECTRONICS ACTIVITY V B CHANDRATRE Head Micro Electonics Section and Project Manager CMEMs ECIL Electronics Division v.b.chandratre@gmail.com eld03@rediffmail.com. Activities. ASIC DESIGN FULL CUSTOM /MIXED TECHNOLOGY DESIGN (PROCESS/DEVICE/SENSOR) HYBRID MICROCIRCUITS

Activities

E N D

Presentation Transcript

MICROELECTRONICS ACTIVITY V B CHANDRATREHead Micro Electonics Sectionand Project Manager CMEMs ECIL Electronics Division v.b.chandratre@gmail.comeld03@rediffmail.com

Activities • ASIC DESIGN FULL CUSTOM /MIXED • TECHNOLOGY DESIGN (PROCESS/DEVICE/SENSOR) • HYBRID MICROCIRCUITS • DATA ACCQUSITION (CORE STRENGTH HW/SW) • MEMS DESIGN • DEVICE MODELLING AND PDK DESIGN KIT DEVLOPMENT

Facilities CAD TOOLS : ASIC /HMC /MEMS DESIGN TCAD TOOLS : TECHNOLOGY DEVELOPMENT PACKAGING TOOLS SEMICONDUCTOR PARAMETRIC MEASURMENT MODELLING ATE IC TESTING: CUSTOM BUILD

10 SUN WORK-STATIONS 3 fast IBM PC lic server Mentor Graphics HDL flow FPGA/ASIC flow (ModelSim, Leonardo) Full Mixed mode HDL/analog/glue logic simulation support. Full custom/ std cell ASIC backend layout tool SCL C1S/D design kit in Mentor Graphics Tanner Tools , 0.7/0.35/0.5SiGe , SITAR design KIT. ECIL CUSTOMER ID EDA CENTRE NEW ADDITIONS : COMPUTING CLUSTER 16GB RAM 1. SUNFIRE V440 QUAD CPU SUN WORKSTATION : 2nos 2. QUAD XEON PROCESSOR WORK STATION : 2Nos 3. HP IBM PC workstations 2NOS CADENCE, MENTOR, COVENTRE, SOFTWARE

SUNFIREV440 Sparc Solaris 8 Each QUAD processor 16Gb COMPUTING SETUP SUN ULTRA 10 [4] / BLADE [6] Solaris 8 QUAD XEON preprocessor 16 GB MEM LINUX /Win 10/100 LAN Mentor Graphics & cadence License servers WIN XP /Scientific Linux 3 ~~ thin clients in new setup for lowering power consumption minimization & laptops for personal use

Upcoming Facility Packaging Lab at CMEMS Facilities: • Manual Epoxy / Eutectic die bonder • Semi-automatic Wire bonder • Flip chip bonder • Wire pull tester • Plasma cleaner • Curing furnace

Upcoming Facility CMEMS TCAD Lab • Facilities: • A versatile structure editor for specifying device geometries. • Semiconductor process simulation tool, having support for Si, SiGe, strained Si, SiC, GaAs and SOI technologies. • Semiconductor device simulation tool, having support for BJT, CMOS, BiCMOS, HBT, APD, FinFET, power devices, CCDs, solar cells etc. • An efficient framework for seamless integration of data across the above mentioned tools

SILICON DETECTORS • Silicon strip detectors • PIN diode detectors • Photodiodes • Silicon Drift Detectors Applications: Radiation monitoring, Nuclear Physics & High Energy Physics experiments

CMS Preshower Detector End caps of CMS detector will have 4300 silicon strip detectors covering area of about 17 m2 BARC is delivering 1000 detector modules for the CMS preshower Weight -12500 T Dia- 15m Length – 21.5m Magnetic field – 4 Tesla

Strip Detectors for CMS Experiment at LHC, CERN Wafers designed and fabricated during various stages of development 2 1 3 Silicon detectors produced by BARC will cover an area of 39,000 cm2in the CMS detector of LHC Detector module

Strip Detector Specifications Electrical High breakdown voltage Breakdown voltage for all strips >= 300V/500V Low leakage:Total current of all strips <= 10 μA at 300V Uniformity of all strips: Maximum 1 strip with leakage current> 5 μA at 300V Geometrical Tight control over dimensions Length 63.0 +- 0.1 mm Width 63.0 +0.0, -0.1 mm

Silicon Drift Detectors (SDD) • Expected Resolution ~100 eV (PIN diodes: ~2keV) • Low anode capacitance without reducing detector size • SDD device and process development and integration of JFET on the detector completed • Under fabrication in BEL

SDDs SDD Array JFETs Layout of SDD on Wafer

Front end for SDD ASIC new concepts… • Critical for Total Channel Noise ~ 100 e- @ 6us shaping time • A novel scheme • (Adaptive Bias) for Large Linear Feedback Resistance, ~3G to reduce noise Sizing optimization allows low noise Radiation hard design to be implemented Linear resistor w/l < 0.1 ~ 0.01

Mixed full custom CMOS ASIC MPW: SCL process C1D 1.2u RADIATION MONITORING INSTRUMENTS NUCLEAR INSTRUMENTS DETECTOR(S) FROM BEL OCTAL Charge Preamp OCTPREM FRONT END DOSIMETER ASIC. CODA High dynamic range FOR fission Fragments charge particle array X-RAY/GAMMA RAY IMAGING MEDIUM DYNAMIC RANGE 8 CHANNEL SILICON STRIP PULSE PROCESSOR. SPAIR 8 CHANNEL CURRENT PULSE PREAMPLIFIERMICON

Octal Pre-amplifier ASIC CHARGE GAIN 1-0.5 V/cC FALL TIME 100/50 uS LINEARITY 1 –0.5% NOISE 400e- SUPPLY 2.5V DRIVE 50 OHMS POWER DISSIPATION 0.9mW OPEN LOOP GAIN 73dB PHASE MARGIN 60 UNITY-GAIN-BANDWIDTH 45MHz Die Area: 2.4 x 1.8 mm2

CODA Co-chip for Dosimeter Application

I to V & SHAPER/ Buffer MICON ref Erroramp in out FICON bias KEY FEATURES LEAKAGE CURRENT COMPENSATION IDEAL FOR PROPORTIONAL CHAMBERS, GEM, PMTS 50 NS PEAKING TIME 1800 e RMS noise 8 CHANNELS WITH SERIAL ANALOG READOUT

Indiplex and Singleplex ASICS Sub-micron 0.7u CMOS process INDIPLEX:16 channel pulse processing ASIC comprising CSA, PZ-block & Semi Gaussian shaper. SINGLEPLEX: Single pulse processing channel ASIC similar to INDIPLEX High Dynamic Range (+/- 600fC) Low Noise with Low Noise Slope (600e @0pf , 7e/pf Noise slope) Output Signal Swing +/-2V Active DC pedestal cancellation. Optimized for Proportional pad detectors made BY VECC for ALICE experiment at CERN.

Block Diagram-Single Channel Charge Sensitive Pre-amplifier Track & Hold CSA DCON Input SHAPER + T&H - De-convolution DC-CAN Active Pedestal Cancellation

VDD Buffer OTA RCM VSS Window Comparator & Control Logic Shaper & Amplifier Base Line Restorer Anu-Shikhar ASIC : CMOS Peak Detect & Hold Circuit With SOC Output Logic • Salient Features : • * Single shaper & amplifier stage at the input with adjustable gain. • * Minimized Pedestal due to Base Line Restoration. • * Reduced Charge Injection by using Rectifying Current Mirror in place of diode in Peak • Detector, also providing complete compatibility with standard CMOS process. • Built in Linear Gate for pulse pile-up rejection. • Dynamic Pedestal correction , • check new concept Dump Current LLD ULD SOC IN Peak Detector Anu-Shikhar ASIC

Anu-Shikhar ASIC ( Pulse peak detector ) • Peak Detect & Hold Circuit with “Start Of Convert” generation Logic for • Nuclear ADC. • Specifications • Dynamic Range -300mV to -1.8V • Power supply +/- 2.5V • Power Consumption 36mW • Droop Rate 0.13V/s (Simulated) • Die Size & Package • 3.3 X 3.3 mm2 ; 44-pin CLCC

VDD Buffer OTA RCM VSS CLK Peak Detect & Hold Ckt Window Comp & Control Logic Pedestal Adjust & BLH I/P GTD_CLK Discharge Current SOC D0-D11 Gray Counter Linear Discharge Source SROUT Shift Register SR CLK Nuclear CMOS ADC for Portable Spectrometer NuCAPS) ASIC Design Specification : • Adjustable Resolution 8/10/12-bit • Frequency of Operation External : 50MHz, Effective : 100MHz • Conversion Time 2.56/10.24/40.96us • Power Consumption 32mW • Input Dynamic Range 20mV-2V(100/1) • DNL 1% of LSB • Die Size 3.5mmX3.5mm

Transient Analog Waveform memory @ 500MS High-Speed Analog Waveform Sampler 128-cell analog waveform sampler with sampling rate of 500MHz.Facilitates High resolution digitization at High Sampling Rates. 2 GHz design in progress • Digital DELAY LOCK LOOP BASED

ASICS in 0.35 /.5 SiGe submicron Extended & closed gate radiation hard MOSFET • IN PIPELINE ……….. • TDC DLL (digital delay lock loop) based • Fast Comparator (Td & Tr) • Si PMT & APD • Radiation Hard Electronics • (design & process ??) • Waiting for the facility to be UP

HYBRIDS …. Production mode TIME TO AMPLITUDE T.A.C HYBRIDS FS 500NS-10U FS 5V RESOLUTION 75PS @ 500NS FS FAST PULSE AMPLIFIER Tr/Tf < 2NS@2V 50 OHMS GAIN 10 O/P DC STABILIZED (HIGH COUNT RATE) Peak stretcher for 8K Nuclear ADC CHARGE SENSITIVE AMPLIFIER BMC1521 1V/PC GAIN 2 keV NOISE FET EXTERNAL VOLTAGE MULTIPLIER INVERTER DRIVER AND SHUT DOWN CIRCUITRY ERROR AMPLIFIER OVERLOAD / OVER VOLTAGE PROTECTION CIRCUITRY AND SHUTDOWN LOGIC O/P VOLTAGE SENSE AND LOAD CURRENT MEASUREMENT CIRCUITRY Use in CAMAC/NIM Modules HIGH VOLTAGE HYBRIDS for Grace Experiments

ASIC IN HYBRIDS ! Hybrids & ASIC …. Indian neutrino Observatory Gas RPC Fast Preamp family tr 1.5 ns… 27,000 Qty requirement Low power pulse channels for portables designs. Trans-impendence Preamp current pulse applications Many Hybrids have High Production Volumes Users NSC, TIFR, VECC, CAT BARC, etc ~ 5 cr account “Singleplex” ASIC in Hybrid For Neutron Monitors

THANK YOU Ack:Menka Tewani, Anubha Tewari, Vangnayee Sharma Nidhi Gupta , Sudheer M , R S Sastrakar, Viashali S & P K Mukhopadhayay Email : v.b.chandratre@gmail.com

New facility :CMEMS GROUND FLOOR • Device Characterization, modeling & ATE • Packaging laboratory FRIST FLOOR • IC design Software for VLSI (VLSI EDA LAB) • TCAD Lab • Embedded development & testing System LAB • Auxiliary facilities