Extensions to the Multicycle CPU

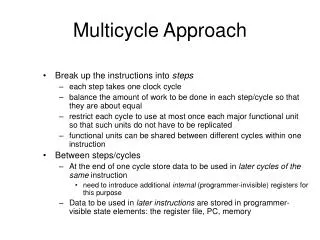

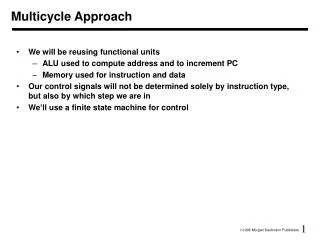

Extensions to the Multicycle CPU. Additional Instructions Exceptions. addi. No new circuits needed third state (after instruction decode) is the same as for lw/sw add the register and the sign-extended immediate fourth state is similar to R-type write-back but RegDst must be 0

Extensions to the Multicycle CPU

E N D

Presentation Transcript

Extensions to the Multicycle CPU Additional Instructions Exceptions

addi • No new circuits needed • third state (after instruction decode) is the same as for lw/sw • add the register and the sign-extended immediate • fourth state is similar to R-type write-back • but RegDst must be 0 • call this new state 10

bne • branch off zero line with a not • combine this line with the zero line in a MUX • send result to AND gate with PCWriteCond • control with new control line called bne • 0 to select beq, 1 to select bne • FSM needs a new state similar to Branch completion • add the control bne = 1, call this state 11 • in the existing branch completion, set bne = 0

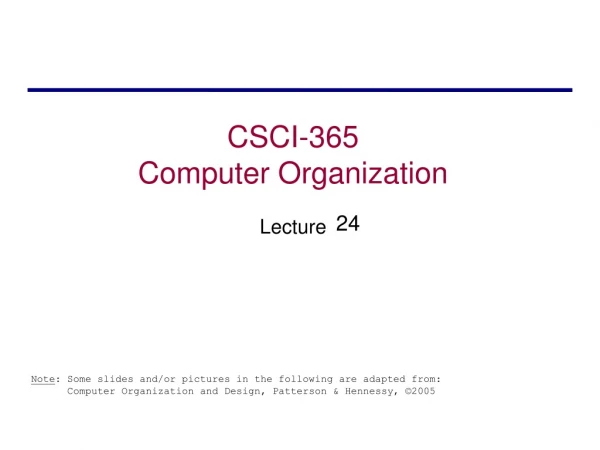

ALU Out Shift Left 2 1 0 PC IR Shift Left 2 Sign Ext ALU Ctrl PCWriteCond PCSrc Control 31-26 0 1 2 bne PCWrite 25-0 PC 31-28 MemWrite Zero ALUSrcA MemRead IorD IRWrite RegDst RegWrite 0 1 0 1 25-21 Read Reg 1 Read/Write Addr Read Data 1 A A L U 20-16 Read Reg 2 Memory Registers 0 1 Read Data 2 B 0 1 2 3 Write Reg Mem Data 4 Write Data Write Data 15-11 0 1 ALUSrcB Mem Data Reg 15-0 MemtoReg 5-0 ALUOp

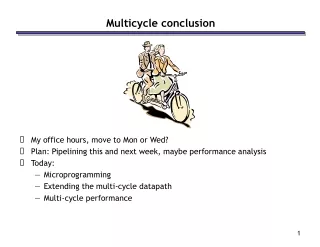

Finite State Machine with addi, bne Instruction Fetch 0 Instruction Decode 1 MemRead IorD = 0 IRWrite ALUSrcA = 0 ALUSrcB = 01 ALUOp = 00 PCSrc = 00 PCWrite ALUSrcA = 0 ALUSrcB = 11 ALUOp = 00 Start lw or sw or addi R-type j ALUSrcA = 1 ALUSrcB = 10 ALUOp = 00 Memory Address Comp 2 bne beq ALUSrcA = 1 ALUSrcB = 00 ALUOp = 10 PCWrite PCSrc = 10 Execution 6 addi Jump Completion 9 ALUSrcA = 1 ALUSrcB = 00 ALUOp = 01 PCWriteCond PCSrc = 01 bne = 1 lw sw RegDst = 0 RegWrite MemtoReg = 0 Write Back 10 Memory Access lw 3 MemRead IorD = 1 ALUSrcA = 1 ALUSrcB = 00 ALUOp = 01 PCWriteCond PCSrc = 01 bne = 0 MemWrite IorD = 1 RegDst = 1 RegWrite MemtoReg = 0 Memory Access sw 5 Branch Completion 11 Write Back 7 RegWrite MemToReg = 1 RegDst = 0 Write Back 4 Branch Completion 8

Exceptions • Unexpected or Unscheduled event which causes a change in the flow of instructions • Examples: • Internal • Non-existent opcode • Integer overflow • Program request to operating system • External Interrupt • I/O request • Hardware malfunction • Requires change in instruction sequence

Exception Handling - Multicycle • Detection and Cause • non-existent opcode -- control • overflow -- signal from ALU • I/O request -- external signal • set register to record cause • Save location in program (address of current instruction) • register (EPC), needed • Change control to exception handling code • enter address of exception code into PC

Exception Circuitry - Multicycle • Overflow signal to control • to detect overflow • Register to save address of current instruction • EPC (Exception Program Counter) • Register to record the cause of the exception • As many bits as needed to record the different types of exception • 32 bits in MIPS, but not all bits are used • Called Cause register • Address of exception code through MUX to PC • Selected by PCSrc, choice 11

CauseWrite ALU Out EPC C a u s e 1 0 PC IR Shift Left 2 Sign Ext ALU Ctrl PCWriteCond PCSrc Control 31-26 0 1 2 3 4 bne PCWrite Shift Left 2 25-0 C0000000 PC 31-28 MemWrite Zero ALUSrcA MemRead EPCWrite IorD IRWrite RegDst RegWrite 0 1 0 1 Overflow 25-21 Read Reg 1 Read/Write Addr Read Data 1 A A L U 20-16 Read Reg 2 Memory Registers 0 1 Read Data 2 B 0 1 2 3 Write Reg Mem Data 4 Write Data Write Data 15-11 IntCause 0 1 ALUSrcB Mem Data Reg 0 1 0 1 15-0 MemtoReg 5-0 ALUOp

Finite State Machine with exceptions 13 0 ALUOp = 01 ALUSrcA = 0; ALUSrcB = 01 IntCause = 0; CauseWrite EPCWrite; PCWrite PCSrc = 11 1 Instruction Fetch Instruction Decode/ Register Fetch Start other Ops lw or sw or addi rfe R-type j Mem Addr Comp or Addi Exe 2 bne beq R-Type Execute 6 PCWrite PCSrc = 100 jump completion addi 9 bne completion lw sw Write-back addi 10 3 Mem Access lw beq completion Mem Access sw Write-back R-Type 5 11 7 14 Write-back 4 8 Overflow ALUOp = 01 ALUSrcA = 0; ALUSrcB = 01 IntCause = 1; CauseWrite EPCWrite; PCWrite PCSrc = 11 12

Exception Code • Located a fixed memory location • 0xC0000000 • Must first save state (as with any function call) • At end must restore state • Decodes Cause Register to determine type of exception • branches to appropriate code • Some exceptions cause program to be aborted • print appropriate error message

Exception Code • Some exceptions take an action • run code to handle input from disk/keyboard/mouse • run code to handle output to screen/other device • The return control to previous program • restore state • rfe (return from exception) • put the address held in the EPC back into the PC • previous program continues from point where it was interrupted