16-bit 4-stage Pipelined Microprocessor

100 likes | 274 Vues

16-bit 4-stage Pipelined Microprocessor. EECS 427 Project Group: JARS ( J ohn, A bhishek, R amashis, S yed). Block Diagram. DATAPATH. CONTROLLER. On-Chip Memory (ROM). On-Chip Memory (RAM). I/O. Stage 4 (Register Write-back and PC Update)

16-bit 4-stage Pipelined Microprocessor

E N D

Presentation Transcript

16-bit 4-stage Pipelined Microprocessor EECS 427 Project Group: JARS (John, Abhishek, Ramashis, Syed)

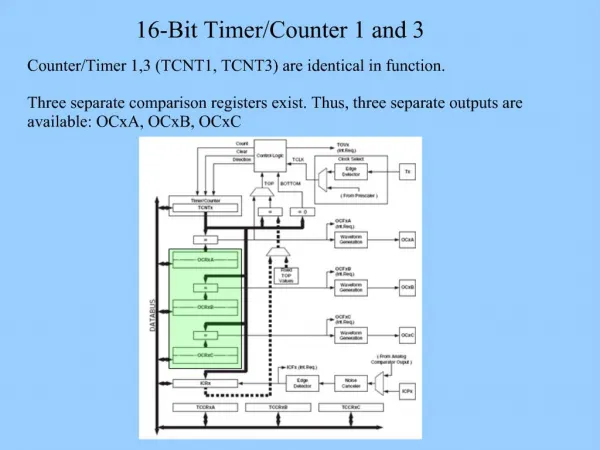

Block Diagram DATAPATH CONTROLLER On-Chip Memory (ROM) On-Chip Memory (RAM) I/O

Stage 4 • (Register Write-back and PC Update) • Writes back the result in Destination Register • In case of Jump, it loads PC with the new value PC IR PC RegA RegB Write Back Data Jump Target Write Jump MUX +1 SHIFTER MUX ALU MUX Register File Instr Mem (ROM) Sign Extend Data Memory (RAM) • Stage 3 • (ALU, Shifter, Memory Access) • Operands are properly chosen and fed into the ALU, Shifter and Memory units • Tri-state MUX is used to select the correct result to be fed into the data-bus • Provision for data-forwarding • PSR calculations and Branch Prediction done Datapath – 4 Stages • Stage 2 • (Instruction Decode and Register Fetch) • Instruction is Decoded in controller • Operands for current Instruction is fetched from Register file/Instruction • In case of Bypass, value is forwarded from previous instruction Stage 1 (Instruction Fetch) Sends PC to Instruction Memory Gets the Instruction Increments PC to PC+1

External Read/Write • Store and Load instructions are slightly modified to incorporate I/O from outside. • Output Instruction: • Store r0, rn %% rn – contains address of data memory from where data has to be sent. • ‘r0’ tells controller that it is an external output. • Input Instruction: • Load raddr’, r1 %% raddr’[9] = ‘1’ which tells controller to store external data to memory address raddr’[8:0]. (Note: 9th bit is unused for normal load operation as we are using 512 RAM) • Idle-waitinghas been implemented to wait for data till it is available to the μP.

RAM RAM I/O Selector Output Buffer DATA IN Output Ready DATA OUT Data Out Inside Chip Outside world

+1 P C Instruction Memory I R load_enable Interrupt Controller Input Ready Data Input (Idle waiting)

Project Done! • DRC & LVS checked layout of μP without on-chip memory. • DRC checked layout of μP with memory. • Memory mapped data I/O with idle-waiting implemented. • DFT: All internal datapath registers are part of Scan chain which facilitates testing.

Thank You - JARS