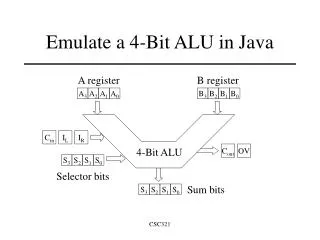

4 Bit ALU

4 Bit ALU. Geeping (Frank) Liu, Kasem Tantanasiriwong, Kuo Hao Huang, Win Pratchayakun Group 18 Advisor: Dave Parent 12-1-2004. Abstract. We designed a functional equivalent 74HC/HCT181 4-bit ALU that can operate at 200 MHz.

4 Bit ALU

E N D

Presentation Transcript

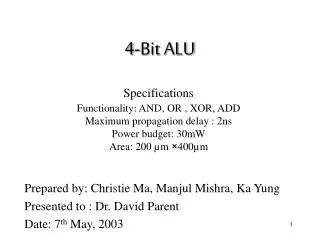

4 Bit ALU Geeping (Frank) Liu, Kasem Tantanasiriwong, Kuo Hao Huang, Win Pratchayakun Group 18 Advisor: Dave Parent 12-1-2004

Abstract • We designed a functional equivalent 74HC/HCT181 4-bit ALU that can operate at 200 MHz. • All inputs (14) and outputs (8) of our design are connected via D flip flops. • Total area is 390x310mm2 • Power dissipation is 14.5mW, with power density of 11.9mW/cm2

Introduction CMOS design has been favored by industry due to its ability to produce high-speed and high density logic circuits. This project provides important background of CMOS design based on NMOS and PMOS characteristics. Students gain the concept of design flow as well as learning the Cadence software tools. These skills may be useful in their future careers.

4 bit ALU Features • Full carry look-ahead for arithmetic operation • Total 16 arithmetic operations (add, subtract, plus, shift, plus 12 others) • Total 16 logic operations (XOR, AND, NAND, NOR, OR, plus 11 others) • Capable of active-high and active-low operation .

Schematic • Logic schematic with worst case path • Allocated different times for different logic levels. • (Inverter requires much less time then a AOI) • Total time allocated to combinational logic=3.2ns • Total time allocated to each FF=.9ns

Design Flow Project specification Functions,CLK speed, Area, Power Logic function level 74HC/HCT181 ALU (Philips) Logic verification through Verilog w/schematic Transistor design level Timing, Sizing design for each building block Timing, power verification Layout design level Layout for each block w/ DRC & LVS verification Design a floor plan to optimize the overall area Post extracted level Final logic & timing verification Towards Schematic v.s. Layout

Critical Path Sizing Methodology :5.0 ns/(7 logic levels + 4 FF levels) =0.46 ns *Cint=40fF *Uses Inv1 sizing for internal inv

Transistor Sizing * Non critical components were tested individually, assuming worst case scenario.

FF Sizing * Cin of DFF=12fF

Simulations (Logic function) A3A2A1A0 = 1010 B3B2B1B0 = 1001 M=1 Cin=1 --------------------------- S3S2S1S0 = 0000 A’ = 0101 S3S2S1S0 =0110 A XOR B = 0011 S3S2S1S0 =1011 A AND B = 1000 S3S2S1S0 =1110 A OR B = 1011

Simulations (Arithmetic function) A3A2A1A0 = 1010 B3B2B1B0 = 1001 M=0 Cin=1 -------------------------------- S3S2S1S0 = 0110 A minus B minus 1= 0000 S3S2S1S0 =1001 A plus B = 0011 S3S2S1S0 =1100 A plus A (shift left) = 0100 S3S2S1S0 =1111 A minus 1 = 1001

Power Power = 58 mW/ 4 clocks = 14.5mw

Lessons Learned • Use Cell based design, LVS and DRC often to avoid potential problems in the future. • Keep good documentation of your design! • Time and work management is vital. • When doing layout for each component, consider how the component will be connected in the overall circuit. • Define specifications for each cell layout such as cell size and output/input locations before starting layout. • Have a idea of overall floor plan before you layout. Decide how the signals will be routed. • Model interconnect capacitance in your schematic.

Summary • Our design met all the specifications, speed 200Mhz, area 390um*310um, power dissipation 14.5 mW, Power density 11.9 W/cm2 • This project provided some insight of the various aspects of the design process. By doing the design, we understand many of the problems design engineers face. • As feature size decreases, factors such as interconnect and parasitic capacitance will have a bigger impact on design

Acknowledgements • Professor Parent • Thanks to Hummingbird for the great remote login. • Thanks to Cadence Design Systems for the VLSI lab • Thanks to my great group members! • Dakao Sandwiches