Electronics for the MEG experiment at PSI

280 likes | 303 Vues

This provides a short introduction to the trigger and DAQ electronics for the MEGAMMA collaboration at the Paul Scherrer Institute. It includes information on the kinematics, search for m -> e gamma down to 10^-14, detector design and tests, trigger electronics, and DAQ electronics.

Electronics for the MEG experiment at PSI

E N D

Presentation Transcript

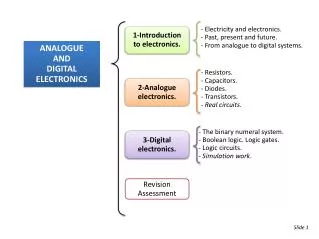

Electronics for the meg experimentat PSI • Short introduction • Trigger electronics • DAQ electronics • Slow Control For the MUEGAMMA collaboration Stefan Ritt (Paul Scherrer Institute, Switzerland)

Kinematics qeg= 180° m e g Ee = 52.8 MeV Eg = 52.8 MeV Search for meg down to 10-14 • LFV Process forbidden by SM • n oscillations expected to enhance LFV rate • Present limit: 1.2 • 10-11 (MEGA) • SUSY Theories: ~ 10-12 • Required: • m+ stopping rate: 108/s • Resolutions (all FWHM): • DEe: 0.7% • DEg: 1.4% @ 52.8 MeV • Dqeg: 12 mrad • Dteg: 150ps MEG Detector

Tests & Design 2002 Assembly 2003 Engineering Run 2004 2005 Data taking 2006 2007 Detector Design . . . 1m

Status Large Prototype • Currently largest LXe detector in (224 PMTs, 150l), • Contains all critical parts of final detector • Currently tested with 40 MeV g’s in Tsukuba, Japan • First results in energy and position resolution expected next weeks

Kinematics qeg= 180° m e g Ee = 52.8 MeV Eg = 52.8 MeV Trigger Requirements • Total ~800 PMTs • Common noise contributes significantly to analog sum • AC coupling Baseline drift • How to evaluate q,f of shower center? • Beam rate 108 s-1 • Fast LXe energy sum > 45MeV 2103 s-1 • g interaction point • e+ hit point in timing counter • time correlation g – e+ 200 s-1 • angular corrlation g – e+ 20 s-1 M.C.

100MHz 10bit 100MHz 10bit 100MHz 10bit FADC FADC FADC 3.3V 2.5V 3.3V 2.5V 3.3V 2.5V VME Interface (Cypress) VME Interface (Cypress) VME Interface (Cypress) FADC FADC FADC FADC FADC FADC FPGA FPGA FPGA FADC FADC FADC FADC FADC FADC FPGA FPGA FPGA SRAM SRAM SRAM FADC FADC FADC FADC FADC FADC FADC FADC FADC FPGA FPGA FPGA SRAM SRAM SRAM FPGA FPGA FPGA LVDS LVDS LVDS LVDS LVDS LVDS LVDS LVDS LVDS 48 bits output 48 bits output 48 bits output Digital Trigger Type1 Type2 LVDS 3.3V 2.5V VME Interface (Cypress) LVDS 100MHz 10bit 8 channels LVDS FPGA FADC 3.3V 2.5V VME Interface (Cypress) LVDS FADC FADC FPGA LVDS FPGA FADC SRAM LVDS 8 channels LVDS FADC FPGA SRAM LVDS FADC FPGA SRAM FADC LVDS FADC FPGA SRAM LVDS FPGA LVDS LVDS LVDS LVDS clck, clear FPGA LVDS LVDS LVDS 48 bits output • All PMTs in trigger • Board hierarchy with LVDS interconnect • Use FPGA with double capacity

Baseline Subtraction Baseline Subtraction 100 MHz Clock 10 bit Latch Latch Latch Latch Calibrated and linearized signal Baseline subtracted signal + Latch LUT 10x10 S - S S - + Uses ~120 out of 5000 logic cells 8 channels/FPGA use 20% of chip S S Latch Baseline Register <thr

QT Algorithm original waveform t • Inspired by H1 Fast Track Trigger (A. Schöning) • Hit region defined when Difference of Samples is above threshold • Integration of original signal in hit region • Pedestal evaluated in region before hit • Time interpolated using maximum value and two neighbor values in LUT 1ns resolution for 10ns sampling time Region for pedestal evaluation integration area smoothed and differentiated (Difference Of Samples) Threshold in DOS 10ns

ADC BS S ADC BS S >45MeV ADC BS S ADC BS . . . AND . . . . . . Max Max Df Max fe+ 10 stages = 1024 chn T[ns] 0 50 100 110 120..200 220 230 Trigger latency • ~600 chn. / 10 bit • At 100 MHz • 75 GB/s processing power In 2 VME crates Inter-board communication: 120ns Total: 350ns (simulated)

Prototype board • Trigger built by INFN, Pisa • Fully simulated FPGA Signal- Generator ADC DAC

m e DAQ Hardware Requirements n PMT sum 0.511 MeV meg 51.5 MeV menng 50 51 52 E[MeV] t ~100ns (menn)2 + g • g’s hitting different parts of LXe can be separated if > 2 PMTs apart (15 cm) • Timely separated g’s need waveform digitizing > 300 MHz • If waveform digitizing gives timing <100ps, no TDCs are needed g e m

pb Domino Sampling Chip • Existing: • 0.5 – 1.2 GHz sampling speed • 128 sampling cells • Readout at 5 MHz, 12 bit • ~ 60 $/channel • Needed: • 2.5 GHz sampling speed • Circular domino wave • 1024 sampling cells • 40 MHz readout • < 100ps accuracy C. Brönnimann et al., NIM A420 (1999) 264

input New Domino Ring Sampler (DRS) • Free running domino wave, stopped with trigger • Sampling speed 2 GHz (500ps/bin), trigger gate sampling gives 50ps timing resolution • 1024 bins 150ns waveform + 350ns delay

DAQ Board • 9 channels 1024 bins / 40 MHz = 230 ms acceptable dead time • Zero suppression in FPGA • QT Algorithm in FPGA (store waveform if multi-hit) • Read out through VME or LVDS domino wave 8 channel DRS 3.3V 2.5V VME Interface (Cypress) 3 state switches 8 channel DRS FPGA FADC 40 MHz 12 bit 8 channel DRS 8 inputs FADC SRAM 8 channel DRS FPGA FADC FPGA SRAM trigger gate Trigger Input SRAM Board inter-connect SRAM shift register Trigger BUS (2nd level tr.) SRAM

Status DRS • Simulation finished in AMS 0.35m process • Layout started • Switch to 0.25m process • First version summer ’02 • Readout with trigger prototype board • Costs per channel:~25$ (board) + 6$ (chip)

TDC Disc. Scaler ADC Scope “Redefinition” of DAQ DSC ~GHz FADC 100 MHz FPGA SRAM

PC 12:30 12.3 12:45 17.2 13:20 15.2 14:10 17.3 15:20 16.2 18:30 21.3 19:20 18.2 19:45 19.2 Slow Control HV Temperature, pressure, … Valves 12345 Terminal Server PLC RS232 GPIB ??? 15° C Ethernet heater MIDAS DAQ

Slow Control Bus HV Temperature, pressure, … Valves heater MIDAS DAQ

CAN, Profibus, LON available Node with ADC >100$ Interoperatibility not guaranteed Protocol overhead Local CPU? User programmable? How to integrate in HV? (CAEN use CAENET) Field Bus Solutions

ADuC812 / C8051F000 Micro controllers RS485 over flat ribbon Flat ribbon connector Power through bus Costs ~30$ Piggy back board Generic Node

Generic node with signal conditioning Sub-master with power supply and PC connection (Parallel Port, USB planned) Integration on sensors, in crates RS232 node planned Crate Oriented • 19” crate with custom backplane • Generic node as piggy-back • Cards for analog IO / digital IO / °C / 220V • crate connects to parallel port (USB) 2 versions BUS Oriented

Midas Slow Control Bus • 256 nodes, 65536 nodes with one level of repeaters • Bus length ~500m opto-isolated • Boards for voltage, current, thermo couples, TTL IO, 220V output • Readout speed: 0.3s for 1000 channels • C library, command-line utility, Midas driver, LabView driver • Nodes are “self-documenting” • Configuration parameters in EEPROM on node • Node CPU can operate autonomously for interlock and regulation (PID) tasks (C programmable) • Nodes can be reprogrammed over network http://midas.psi.ch/mscb

High Voltage System External HV mC node Opto-couplers

Regulates common HV source 0-2400V, ~1mA DAC 16bit, ADC 14bit Current trip ~10ms Self-calibration with two high accuracy reference voltages Accuracy <0.3V absolute Boards with 12 channels, crates with 192 channels 30$/channel (+ext. HV) HV performance Prototype

Conclusions • FPGA-based trigger with 100MHz FADC designed • 2 GHz waveform sampling on all channels planned • HV system with 0.3V accuracy designed • New slow control system (30$/node, 300ms readout) • Transition prototype series • Physics runs in 2005 • Can be useful for other experiments • In case of interest: stefan.ritt@psi.ch Transparencies on Muegamma Web Site: http://meg.psi.ch