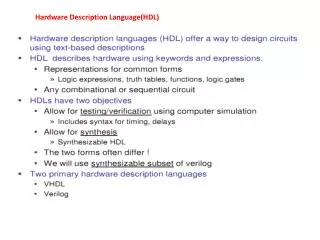

Hardware Description Language(HDL)

570 likes | 946 Vues

Hardware Description Language(HDL). History of Verilog.

Hardware Description Language(HDL)

E N D

Presentation Transcript

History of Verilog Verilog simulator was first used beginning in 1985 and was extended substantially through 1987. The implementation was the Verilog simulator sold by Gateway. The first major extension was Verilog-XL, which added a few features and implemented the infamous "XL algorithm" which was a very efficient method for doing gate-level simulation. The time was late 1990. Cadence Design System, whose primary product at that time included Thin film process simulator, decided to acquire Gateway Automation System. Along with other Gateway products, Cadence now became the owner of the Verilog language, and continued to market Verilog as both a language and a simulator. At the same time, Synopsys was marketing the top-down design methodology, using Verilog. This was a powerful combination.

History of Verilog Continued------ In 1990, Cadence recognized that if Verilog remained a closed language, the pressures of standardization would eventually cause the industry to shift to VHDL. Consequently, Cadence organized the Open Verilog International (OVI), and in 1991 gave it the documentation for the Verilog Hardware Description Language. This was the event which "opened" the language. In the meantime, the popularity of Verilog and PLI was rising exponentially. Verilog as a HDL found more admirers than well-formed and federally funded VHDL. It was only a matter of time before people in OVI realized the need of a more universally accepted standard. Accordingly, the board of directors of OVI requested IEEE to form a working committee for establishing Verilog as an IEEE standard. The working committee 1364 was formed in mid 1993 and on October 14, 1993, it had its first meeting.

Properties of Verilog • Case Sensitivity • Verilog is case sensitive. • White Space Characters • blanks, tabs, newlines (carriage return), and form feeds. • Comments • // begins a single line comment, terminated by a newline. • /* begins a multi-line block comment, terminated by a */. • Attributes • (* begins an attribute, terminated by a *). • • An attribute specifies special properties of a Verilog object or statement, for use by specific software tools, such as synthesis. Attributes were added in Verilog-2001. • • An attribute can appear as a prefix to a declaration, module items, statements, or port connections. • • An attribute can appear as a suffix to an operator or a call to a function. • • An attribute may be assigned a value. If no value is specified, the default value is 1. • • Multiple attributes can be specified as a comma-separated list. • • There are no standard attributes in the Verilog-2001 standard; Software tools or other standards will define attributes as needed.

Identifiers (names) • Must begin with alphabetic or underscore characters a-z A-Z • May contain the characters a-z A-Z 0-9 _ and $ • May use any character by escaping with a backslash ( \ ) at the beginning of the identifiers and terminating with a white space. • Identifiers created by an array of instances or a generate block may also contain the characters [ and ].

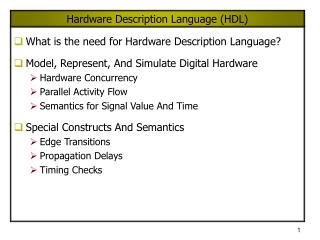

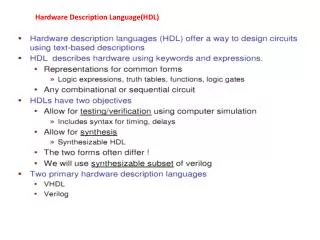

Verilog syntax and language constructs are designed to facilitate description of hardware components for simulation and synthesis. In addition‚ Verilog can be used to describe test-benches‚ specify test data and monitor circuit responses.

Verilog is one of the HDL languages available in the industry for designing the Hardware. Verilog allows us to design a Digital design at • Behavior Level, • Register Transfer Level (RTL), • Gate level and at switch level. • Verilogallows hardware designers to express their designs with behavioral constructs, deterring the details of implementation to a later stage of design in the final Design Styles: Verilog like any other hardware description language, permits the designers to design a design in either Bottom-up or Top-down methodology.

Bottom-UP design The traditional method of electronic design is bottom-up. Each design is performed at the gate-level using the standard gates With increasing complexity of new designs this approach is nearly impossible to maintain. New systems consist of ASIC or microprocessors with a complexity of thousands of transistors. These traditional bottom-up designs have to give way to new structural, hierarchical design methods. Without these new design practices it would be impossible to handle the new complexity.

Top-Down Design The desired design-style of all designers is the top-down design. A real top-down design allows early testing, easy change of different technologies, a structured system design and offers many other advantages. But it is very difficult to follow a pure top-down design. Due to this fact most designs are mix of both the methods, implementing some key elements of both design styles.

Module The entity used in Verilog for description of hardware components is a module. A module can describe a hardware component as simple as a transistor or a network of complex digital systems. As shown in Figure given below‚ modules begin with the module keyword and end with endmodule. Module Hierarchy

Module Port: Following the name of a module is a set of parenthesis with a list of module ports. This list includes inputs‚ outputs and bidirectional inputlines. Ports may be listed in any order. This ordering can only become significant when a module is instantiated‚ and does not affect the way its operation is described. Top-level modules used for testbenches have no ports.

Wire: • Nets are used connect structural components together • A net data type must be used when a signal is: • driven by the output of a module instance or primitive instance. • Connected to an input or inout port of the module in which it is declared. • On the left hand side of a continuous assignment • Net type is one of the following keywords Wire:

Figure given below shows an example circuit with scalar‚ vectored‚ input‚ output and inout ports. Ports named a‚ and b are one-bit inputs. Ports av and bv are 8-bit inputs of acircuit. The set of square brackets that follow the input keyword applies to all ports that follow it. Port w of ac ircuit is declared as a 1-bit output‚ and wv is an 8-bit bi-directional port of this module.

Wire and Variable declaration: • In addition to port declarations‚ a module declarative part may also include wire and variable declarations that are to be used inside the module. Wires (that are called net in Verilog) are declared by their types‚ wire‚wand or wor; and variables are declared as reg. • Wires are used for interconnections and have properties of actual signals in a hardware component. • Variables are used for behavioral descriptions and are very much like variables in software languages. Figure 3.9 shows several wire and variable declarations

Variable data types are used for programming storage in procedural blocks. • Variables store logic values only, they do not store logic strength. • A variable data type must be used when the signal is on the left-hand side of a procedural assignment. • Variables were called “registers” in older versions of the Verilog standard. Variable _type is one of the following

Wires represent simple interconnection wires‚ busses‚ and simple gate or complex logical expression outputs. • When wires are used on the left hand sides of assign statements‚ they represent outputs of logical structures. Wires can be used in scalar or vector form. Figure given below shows several examples of wires used on the right and left hand sides of assign statements

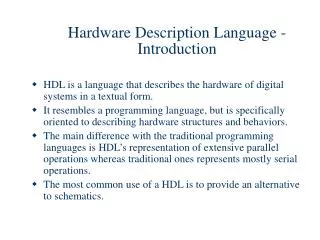

Verilog Verilog is a HARDWARE DESCRIPTION LANGUAGE (HDL). A hardware description Language is a language used to describe a digital system, for example, a microprocessor or a memory or a simple flip-flop. This just means that, by using a HDL one can describe any hardware (digital ) at any level.

Basic building block in Verilog. • Module • 1. Created by “declaration” (can’t be nested) • 2. Used by “instantiation“ • Interface is defined by ports • May contain instances of other modules • All modules run concurrently Instances A module provides a template from which you can create actual objects.

When a module is invoked, Verilog creates a unique object from the template. • Each object has its own name, variables, parameters and I/O interface.

Test Bench: Design Model Synthesis Net list