Resolving Signals' Correlation in Combinational Equivalence Checking

190 likes | 303 Vues

Explore a probabilistic approach for CEC with non-aliasing assignments, focusing on internal gate replacement strategies and complex reconvergent regions.

Resolving Signals' Correlation in Combinational Equivalence Checking

E N D

Presentation Transcript

Resolving Signals' Correlation in Combinational Equivalence Checking Speaker: Shih-Chieh Wu Advisor: Chun-Yao Wang 2005.10.17

Outline • Introduction • Previous Work • Cut-Points Resolution Problem • Correspondent-Based Cutting Algorithm • Future Work

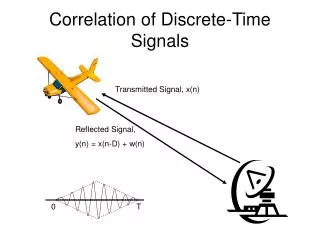

Motivation (1/2) • Probabilistic approach for CEC with non-aliasing assignments • Miter structure • Values can be assigned after complete suppression • Internal equivalent gates replacement • only supergate can be substituted C1 x 0? C2

Motivation (2/2) • The non-aliasing assignments grow exponentially • Resource is limited (18~22 assignments) • Replace the internal equivalent gates for resource re-use • However, the reconvergent region may be complex and large • Out of resource • Replacement is performed near primary output

Problem Formulation • Given two combination circuits C1 & C2, we want to verify if C1≡C2 • Resolving signal's correlation Correlation on ISCAS benchmarks "A Symbolic Simulation Approach in Resolving Signals' Correlation“, Julien Dunoyer, Nizar Abdallah, and Pirouz Bazargan Sabet

Outline • Introduction • Previous Work • Cut-Points Resolution Problem • Correspondent-Based Cutting Algorithm • Future Work

Previous Work • J. Savir, G. S. Ditlow, and P. H. Bardell, " Random pattern testability", IEEE Transactions on Computers, pp. 79-90, January 1984. • Cutting algorithm: operate by cutting the reconvergent fanout branches and by inserting equivalent bounds at the cut points • F. N. Najm, R. Burch, P. Yang, and I. N. Hajj, "Probabilistic simulation for reliability analysis of CMOS VLSI circuits", IEEE Transactions on Computer-Aided Design, pp. 439-450, April 1990 • Based on the supergate concept

Outline • Introduction • Previous Work • Cut-Points Resolution Problem • Correspondent-Based Cutting Algorithm • Future Work

Functional Decomposition • Decompose each function into functional blocks • Represent each block as a BDD (partitioned BDD method) • Define cut-points(z) • Verify equivalence of blocks at cut-points starting at primary inputs F G f2 g2 z z f1 g1 y y x x

Cut-Points Resolution Problem • If all pairs of cut-points (z1, z2) are equivalent • So are the two functions (F, G) • If intermediate functions (f2, g2) are not equivalent • The functions (F, G) may still be equivalent • This is called false negative • Why do we have false negative • Functions are represented in terms of intermediate variables • To prove/disprove equivalence must represent the functions in terms of primary inputs (BDD composition)

x1 Y1 x2 W Y2 x3 x1 C2 Z1 x2 W Z2 x3 Example • False negative as a result of cutting the circuits at nodes (Y1, Z1) and (Y2, Z2) C1 C1: W = Y1⊕Y2 = Y1+Y2-2*Y1*Y2 C2: W = Z1+Z2 = Z1+Z2-Z1*Z2

Outline • Introduction • Previous Work • Cut-Points Resolution Problem • Correspondent-Based Cutting Algorithm • Future Work

Correspondent-Based Cutting Algorithm • Assume that gate G1 in circuit C1 has the same value correspondent to gate G2 in circuit C2 • G1 and G2 are equivalent • If G1, G2 are reconvergent fanout nodes and have the same number of fanouts • G1(i) represent the i-th fanout node of G1 • If the side input of G1(i) has the same value correspondent to the side input of G2(j) • We can cut the correspondent reconvergent fanout by inserting equivalent input signal

Structure Is the Same • Verify C1 and C2 (x3, x2, Y2, x1, Y1, W) x1 x1 C1 C1 C1≡C2 after cutting edge(x2, Y2) in C1 and edge(x2, Z2) in C2 1/5 Y1 Y1 1/3 x2 1/5 x2 x2 W W 1/5 5/15 Y2 Y2 1/3 x3 x3 1/3 1/15 x1 x1 C2 C2 1/5 Z1 Z1 1/3 x2 1/5 x2 x2 W W 5/15 1/3 Z2 Z2 1/5 x3 x3 1/3 1/15

Structure Is Different • Verify C1 and C2 (x3, x2, Y2, x1, Y1, W) x1 x1 C1 C1 False Negative? 1/5 Y1 Y1 1/3 x2 1/5 x2 x2 W W 1/5 6/15 Y2 Y2 1/3 x3 x3 1/3 C1: W = x1- x1*x2+x2*x3 C2: W = x1-x1*x2+x2*x3 1/15 x1 x1 C2 C2 1/5 Z1 Z1 1/3 x2 1/5 x2 x2 W W 5/15 1/3 Z2 Z2 1/5 x3 x3 1/3 1/15

False Negative? Why False Negative Occurs? • 3-vector simulation => 4-vector simulation

Why Substitution Works? • 4-vector simulation => 2-vector simulation C1 x1 x2 f2 x3 f1 x4 C2 x1 x2 f2 x3 f1 x4

Outline • Introduction • Previous Work • Cut-Points Resolution Problem • Correspondent-Based Cutting Algorithm • Future Work

Future Work • Try to eliminate false negatives • Complete experiment for the same structure circuits