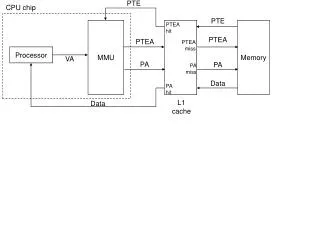

Understanding PTE and MMU Interactions in CPU Memory Management

DESCRIPTION

This article explores the intricacies of Page Table Entries (PTE), the Memory Management Unit (MMU), and their roles in CPU memory operations. Highlighting the distinction between hits and misses, we discuss how virtual addresses (VA) are translated to physical addresses (PA) and the functions of L1 cache in optimizing data access. Insight into PTEA interactions is provided, illustrating how the system handles memory requests, optimization strategies, and performance implications in modern processors.

1 / 1

Télécharger la présentation

Understanding PTE and MMU Interactions in CPU Memory Management

An Image/Link below is provided (as is) to download presentation

Download Policy: Content on the Website is provided to you AS IS for your information and personal use and may not be sold / licensed / shared on other websites without getting consent from its author.

Content is provided to you AS IS for your information and personal use only.

Download presentation by click this link.

While downloading, if for some reason you are not able to download a presentation, the publisher may have deleted the file from their server.

During download, if you can't get a presentation, the file might be deleted by the publisher.

E N D

Presentation Transcript

PTE CPU chip PTE PTEA hit MMU Memory PTEA PTEA miss PTEA Processor VA PA PA PA miss Data PA hit L1 cache Data

More Related