Biasing an MOS Transistor Using g m /I D technique

170 likes | 454 Vues

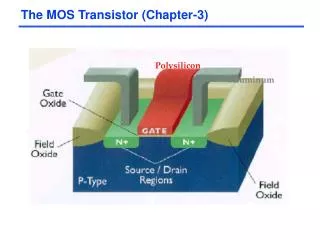

Biasing an MOS Transistor Using g m /I D technique. Section 7.1 J.Ou Sonoma State Univeristy. Basic Analysis. Use 1.2 V. (Modified Ex 7.1). Design Equations. Assumption: VDD=1.2 V. Transistor Information: Type: 120 nm Specify VDS Note var1_1 is ‘vsd’ if pmos is used

Biasing an MOS Transistor Using g m /I D technique

E N D

Presentation Transcript

Biasing an MOS Transistor Using gm/ID technique Section 7.1 J.Ou Sonoma State Univeristy

Basic Analysis Use 1.2 V (Modified Ex 7.1)

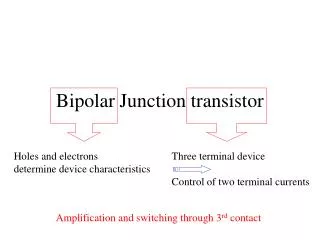

Assumption: VDD=1.2 V Transistor Information: Type: 120 nm Specify VDS Note var1_1 is ‘vsd’ if pmos is used Note var2_1 is ‘vns’ if nmos is used. In this example, is initially unknown, so we will assume that it is 0.0

Interpolation Since the database base can not be so large as to keep all possible values of vds/vsb, we have to interpolate based on existing values, which are available On 0.1 V interval. Current release: need to enter inBias <= the minVar1 and maxVar1.

Browse Database dBrowse2D(25, 'pfet', '15.0u', 'vsd', 0.3, 0.4, 0.353, 'vns', 0.5, 0.6, 0.577, 'vth') Variable name=dBrowse2D(gmoverid, type, length, var1, minVar1, maxVar1,inBias1, var2, minVar2, maxVar2,inBias2, ‘parameter’ ) Valid parameters: gmovergds, gmovergmbs, vth, ft, gmoveridft, idoverw, vod, region, fndbderiv cgdovercgg,cddovercgg, cgsovercgg, csbovercgg, cdbovercgg, ron, vdsat, rseff, rdeff type: nfet, pfet length: {'120n' '180n' '250n' '350n' '600n' '800n' '1.0u' '2.0u' '3.0u' '4.0u' '5.0u' '6.0u' '7.0u' '8.0u' '9.0u' '10.0u' '15.0u' '20.0u'} (text string)

Iteration • Start with • length=‘120nm’ • gmoverid=20 • VDS=VDD/2, VSB=0 • Calculate • vod_1 • vth_ • vgs_1 • vx (gate voltage) • vs (source voltage) • ID • Idoverw • W • RD • Vd • Vds=Vd-Vs