Understanding Sequential Vs. Combinational Logic in Electronic Circuits

E N D

Presentation Transcript

Sequential vs. Combinational • Combinational Logic: • Output depends only on current input • TV channel selector (0-9) • Sequential Logic: • Output depends not only on current input but also on current state of the system (which depends on past input values) • TV channel selector (up-down) • Need some type of memory to remember the current state inputs outputs system

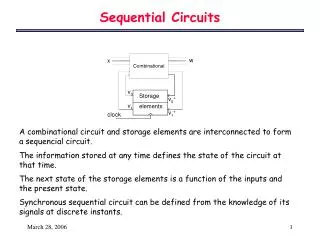

Sequential Logic • Sequential Logic circuits • Remember past inputs and past circuit state. • Outputs from the system are “fed back” as new inputs. • The storage elements are circuits that are capable of storing binary information: memory.

Feedback Loop • Feedback: • A signal s1 depends on another signal whose value depends on s1 • (perhaps with several intermediate signals). s1

Base of Memory • Consider the following circuit: • It can differentiate between two different states as it has only one feedback line that can keep one of two values, 0 or 1. • A circuit with n feedback lines has 2n potential states, and that the memory of our circuit depends on the number of its feedback lines:

Synchronous vs. Asynch. • Synchronous sequential circuit: • the behavior can be defined from knowledge of its signal at discrete instants of time. • achieves synchronization by using a timing signal called the clock. • Asynchronous sequential circuit: • the behavior is dependent on the order of input signal changes over continuous time, and output can change at any time (clockless).

Clock Signal Rising Clock Edge Clock generator: Periodic train of clock pulses Different duty cycles Falling Clock Edge

Clock Signal • Clock is distributed throughout the whole design • All components synchronizes itself with it.

Synchronous Circuits Combinational Logic clk time

R Q R S S Q’ SR latch (NOR version) Truth Table: Next State = F(S, R, Current State) S(t) R(t) Q(t) Q(t+) 0 0 0 0 (hold) 0 0 1 1 (Hold) 0 1 0 0 (reset) 0 1 1 0 (reset) 1 0 0 1 (set) 1 0 1 1 (set) 1 1 0 Not allowed 1 1 1 Not allowed

Characteristic Equation: Q+ = S + R Q t S R-S Latch Q+ R Q SR Latch Truth Table: Next State = F(S, R, Current State) Derived K-Map: S(t) R(t) Q(t) Q(t+) 0 0 0 0 (hold) 0 0 1 1 (Hold) 0 1 0 0 (reset) 0 1 1 0 (reset) 1 0 0 1 (set) 1 0 1 1 (set) 1 1 0 Not allowed 1 1 1 Not allowed

R=S=1 ?? • Illegal output, because • When S=R=1, both outputs go to zero. • If both inputs now go to 0, the state of the SR flip flop is depends on which input remains a 1 longer before making transition to 0. • Hence, “undefined” state. MUST be avoided.

R S Q Q’ Timing Diagram 100 Reset Hold Reset Set Race Set Forbidden State Forbidden State

SR Latch State Diagram • Theoretical State Diagram

Q Q Q Q 1 0 0 1 Q Q 0 0 SR Latch State Diagram • Observed State Diagram • Very difficult to observe R-S Latch in the 1-1 state • Ambiguously returns to state 0-1 or 1-0

S’R’ Latch (NAND version) S’ R’ Q Q’ 0 S’ 1 Q 0 0 0 1 1 0 1 1 1 0 Set 0 Q’ 1 R’ X Y NAND 0 0 1 0 1 1 1 0 1 1 1 0 S Q R-S Latch R Q’

S’R’ Latch (NAND version) S’ R’ Q Q’ 1 S’ 1 Q 0 0 0 1 1 0 1 1 1 0 Set 0 Q’ 1 1 0 Hold R’ X Y NAND 0 0 1 0 1 1 1 0 1 1 1 0

S’R’ Latch (NAND version) S’ R’ Q Q’ 1 S’ 0 Q 0 0 0 1 1 0 1 1 1 0 Set 0 1 Reset 1 Q’ 0 1 0 Hold R’ X Y NAND 0 0 1 0 1 1 1 0 1 1 1 0

S’R’ Latch (NAND version) S’ R’ Q Q’ 1 S’ 0 Q 0 0 0 1 1 0 1 1 1 0 Set 0 1 Reset 1 Q’ 1 1 0 Hold R’ 0 1 Hold X Y NAND 0 0 1 0 1 1 1 0 1 1 1 0

S’R’ Latch (NAND version) S’ R’ Q Q’ 0 S’ 1 Q 1 1 Disallowed 0 0 0 1 1 0 1 1 1 0 Set 0 1 Reset 1 Q’ 0 1 0 Hold R’ 0 1 Hold X Y NAND 0 0 1 0 1 1 1 0 1 1 1 0

SR Latch with Clock signal Latch is sensitive to input changes ONLY when C=1

S CLK R S R CLK S’ R’ Q Q’ SR Latch with Clock signal S’ Q Q’ R’ 0 0 1 1 1 Q0 Q0’ Store 0 1 1 1 0 0 1 Reset 1 0 1 0 1 1 0 Set 1 1 1 0 0 1 1 Disallowed X X 0 1 1 Q0 Q0’ Store

D Latch • One way to eliminate the undesirable indeterminate state in the RS flip flop: • ensure that inputs S and R are never 1 simultaneously. This is done in the D latch: Q D D Latch Q’ C

D D CLK Q Q’ 0 1 0 1 1 1 1 0 X 0 Q0 Q0’ D Latch (cont.) S S’ Q CLK Q’ R R’ S R CLK Q Q’ 0 0 1 Q0 Q0’ Store 0 1 1 0 1 Reset 1 0 1 1 0 Set 1 1 1 1 1 Disallowed X X 0 Q0 Q0’ Store

D Latch Timing Diagram Q D D Latch Q’ C C

D Latch with Transmission Gates 1 2 • C=1 TG1 closes and TG2 opens Q’=D’ and Q=D • C=0 TG1 opens and TG2 closes Hold Q and Q’

Q’ Q ( t ) JK Latch J Q J, K both one yields toggle K J-K Latch Derived K-Map: J(t) K(t) Q(t) Q(t+) 0 0 0 0 (hold) 0 0 1 1 (Hold) 0 1 0 0 (reset) 0 1 1 0 (reset) 1 0 0 1 (set) 1 0 1 1 (set) 1 1 0 1 (toggle) 1 1 1 0 (toggle) J JK 00 01 11 10 0 0 0 1 1 1 1 0 0 1 K Characteristic Equation: Q+ = Q K’ + Q’ J

Q’ Q’ R-S latch JK Latch Using SR Latch How to eliminate the forbidden state in SR? Idea: use output feedback to guarantee that R and S are never both one J, K both one yields toggle K R J S Q Q Characteristic Equation: Q+ = Q K + Q J

JK Lacth Race Condition Reset Set Toggle Toggle Correctness: Single State change per clocking event Solution: Master/Slave Flipflop

Flip-Flops • Latches are “transparent” (= any change on the inputs is seen at the outputs immediately). • This causes synchronization problems! • Solution: use latches to create flip-flops that can respond (update) ONLY on SPECIFIC times (instead of ANY time).

Alternatives in FF choice • Type of FF • RS • D • JK

D-FF Truth table Timing for D Flip-Flop (Falling-Edge Trigger)

Rising Edge D-FF Falling-Edge Circuit?

Setup & Hold Times Setup and Hold Times for an Edge-Triggered D Flip-Flop

Edge-Triggered D Flip-Flop Figure 11-17. Determination of Minimum Clock Period

Master-Slave FF configuration using SR latches • Enables level-triggered behavior

Master-Slave FF configuration using SR latches (cont.) S R CLK Q Q’ • When C=1, master is enabled and stores new data, slave stores old data. • When C=0, master’s state passes to enabled slave (Q=Y), master not sensitive to new data (disabled). 0 0 1 Q0 Q0’ Store 0 1 1 0 1 Reset 1 0 1 1 0 Set 1 1 1 1 1 Disallowed X X 0 Q0 Q0’ Store Slave Master

Master-Slave J-K Flip-Flop 1's Set Reset Catch T oggle 100 J K C P Master outputs P‘ ‘ Q Slave Q’ outputs P P’ Sample inputs while clock low Sample inputs while clock high Uses time to break feedback path from outputs to inputs! Correct Toggle Operation

Edge-Triggered FF 1's Catching: a 0-1-0 glitch on the J or K inputs leads to a state change! forces designer to use hazard-free logic Solution: edge-triggered logic Negative Edge-Triggered D flipflop 4-5 gate delays setup, hold times necessary to successfully latch the input Characteristic Equation: Q+ = D Negative edge-triggered FF when clock is high

T Flip-Flop T Flip-Flop Timing Diagram for T Flip-Flop (Falling-Edge Trigger)

Implementation of T-FF Implementation of T Flip-Flop

FFs with Additional Inputs Figure 11-27. D Flip-Flop with Clock Enable The characteristic equation : The MUX output :

S D Q C Q R Asynchronous Preset/Clear • Many times it is desirable to asynchronously (i.e., independent of the clock) set or reset FFs. • Example: At power-up to that we can start from a known state. • Asynchronous set == direct set == Preset • Asynchronous reset == direct reset == Clear • There may be “synchronous” preset and clear.

S 1J C1 1K R Asynchronous Set/Reset Cn indicates that Cn controls all other inputs whose label starts with n. In this case, C1 controls J1 and K1. Function Table IEEE standard graphics symbol for JK-FF with direct set & reset