Reconfigurable DSP Project: Final Design Review of MPEG II Decoder

This project presents the final design review of an MPEG II Decoder developed by the Decoder Group at Georgia Institute of Technology. Key deliverables included decoding instruction sets for different profiles, defining control signals, and implementing the decoder in VHDL for comprehensive testing. The design employed a state-machine approach, enabling flexibility and reducing controller complexity. The project emphasizes timely task distribution among team members and successful integration with other groups in the course. Lessons learned included addressing technical difficulties and enhancing communication between teams.

Reconfigurable DSP Project: Final Design Review of MPEG II Decoder

E N D

Presentation Transcript

Reconfigurable DSP Project The Choochoo: MPEG II Decoder Final Design Review JAMM – THE DECODER GROUP School of Electrical and Computer Engineering Georgia Institute of Technology FDR--ECE6276 Class Project 12/06/00

Team Members • Sirisha Reddy • Neil Shah • James Tuan • Chris Wood FDR--ECE6276 Class Project 12/06/00

Project Requirements • Decoding Instruction Sets for each Profile. • Defining Control Signals and Reservation Tables • Coding and Testing of the decoders for the three profiles. • Support and Integrate with other groups (ISA, Architecture, and DP1) FDR--ECE6276 Class Project 12/06/00

Task Distribution • Sequential progress from one profile to the other • Met the deadlines in a timely manner FDR--ECE6276 Class Project 12/06/00

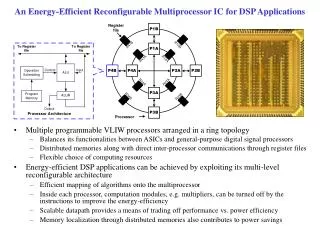

Design Considerations • State Machine Approach • MicroCode • Flexibility in translation • Reduces the complexity of controller • Decreases development time • Field updatable FDR--ECE6276 Class Project 12/06/00

What we have accomplished • Definitions for the control signals. • IDCT profile. • Inverse Quantization • Motion Compensation • Implementation of the decoder (in VHDL) for all the three profiles. • Testing of the three profiles. FDR--ECE6276 Class Project 12/06/00

Support Role • Integration with other groups • Helped DP1 in testing the Profiles. • Architecture • Buses • Multiplexers • Latches • ISA • Minor changes to reduce controller complexity FDR--ECE6276 Class Project 12/06/00

Tests and Results • Tested each profile, • Used Program Memory to cycle through each instruction for each profile. • Generated timing diagrams through VHDL • Verified timing diagrams • Successfully tested the instruction sets FDR--ECE6276 Class Project 12/06/00

Lessons Learned • Technical Difficulties • ISA • Architecture • DP1 • Communicating with other groups FDR--ECE6276 Class Project 12/06/00