Design and Implementation of a Pipelined 32-bit AIE Processor with Instruction Optimization

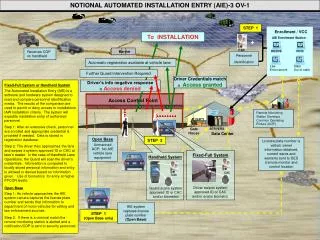

This document outlines the design of a 32-bit pipelined AIE processor, emphasizing its architecture, including fetch, decode, execute, memory access, and write-back stages. It discusses both synchronous and asynchronous pipeline designs, detailing advantages such as reduced clock waste through handshaking signals, alongside challenges like high circuit complexity and implementing queue management. The processor supports 48 instructions, features interleaved memory architecture, and showcases various operation codes, handling immediate, register, and indirect addressing modes.

Design and Implementation of a Pipelined 32-bit AIE Processor with Instruction Optimization

E N D

Presentation Transcript

Sequential Processor Stages Fetch Decode Execute Mem WB

Pipelining Processor Stages Execute Pip E line Mem Pip E line WB Fetch Pip E line Decode Pip E line

Transaction Table Five Stages Pipeline

Pipelining Design • As Queue • Problems: • High Circuit Complexity • If Queue is Full in a stage the previous must halt until the queue release item, so there is no great benefit. • Implementation • Shift Register Circuit & Registers [Waste Cycles] • Counter & Registers [Save Cycles]

Pipeline Optimal Designs • Sync Pipeline • All Pipeline Modules Attached with Same Cycle Controller • Cycle Time = Max Stage Clock • Problems • There is Waste in Clock but not to much • Every stage not aware of the status of previous stage.

Pipeline Optimal Designs • A Sync Pipeline • Every Stage aware of the status of the previous stage using internal handshaking signals • Ready – Acknowledge Signals • Advantages • There is no clock waste thanks to handshaking signals • There is no Max Cycle Clock, every instruction take the clocks need to perform it’s operation. • Disadvantages • In Control Unit you must specify every instruction timing in every stage of the pipelined processor

Pipeline Optimal Designs • Sync Pipeline & A Sync Pipeline

Key Feature of AIE Processor • 32-bit Pipelined Processor • Processor Support 48 Instruction • Processor Interface with Interleaved Memory • Interface with LCD Terminal using Instructions • Processor have it’s Assembly Interpreter

INSTRUCIONS ROM IR Register 8 bit 24 bit Modes Select Address Bus : 8 bit Data Bus : 32 bit 32 bit

00-NOP -00008000 01-MOV reg,immediate -8c005000 02-ADD d.reg,s1.reg,s2.reg -20007000 03-ADC d.reg,s1.reg,s2.reg -22007000 04-SUB d.reg,s1.reg,s2.reg -24007000 05-SUW d.reg,s1.reg,s2.reg -26007000 06-MUL d.reg,s1.reg,s2.reg -28007000 07-DIV d.reg,s1.reg,s2.reg -2a007000 08-TRSA d.reg,s1.reg -2c007000 09-TRSB d.reg,s2.reg -2e007000 0a-AND d.reg,s1.reg,s2.reg -30007000 0b-OR d.reg,s1.reg,s2.reg -32007000 0c-NAND d.reg,s1.reg,s2.reg -34007000 0d-NOR d.reg,s1.reg,s2.reg -36007000 0e-XOR d.reg,s1.reg,s2.reg -38007000 0f-XNOR d.reg,s1.reg,s2.reg -3a007000 10-NOT d.reg,s1.reg -3c007000 11-CMP reg1,reg2 -3e002000 12-IPNT immediate -4c022000 13-RPNT reg -2c022000 14-STOWE address,reg -4c102000 15-STOWO address,reg -4c142000 16-STODW address,reg -4c302000 17-LODWE reg,address -4c195000 18-LODWO reg,address -4c1d5000 19-LODDW reg,address -4c395000 1a-JG address -8c400000 1b-JE address -8c800000 1c-JL address -8cc00000 1d-JC address -8d000000 1e-JNG address -8c400800 1f-JNE address -8c800800 20-JNL address -8cc00800 21-JNC address -8d000800 22-JMP address -8d400000

IMMEDIATE MODE IR Register : ROM- address REG-address IMMEDIATE 8bit 3bit 5 bit 16 bit Instructions : *MOV reg,immediate -8c005000 *JG address -8c400000 *JE address -8c800000 *JL address -8cc00000 *JC address -8d000000 *JNG address -8c400800 *JNE address -8c800800 *JNL address -8cc00800 *JNC address -8d000800 *JMP address -8d400000

REGISTER REGISTER MODE IR Register : ROM- address Destination_REG Source_REG1 Source_REG2 8bit 3bit 5 bit 3bit 5 bit 3bit 5 bit Instructions : *ADD d.reg,s1.reg,s2.reg -20007000 *ADC d.reg,s1.reg,s2.reg -22007000 *SUB d.reg,s1.reg,s2.reg -24007000 *SUW d.reg,s1.reg,s2.reg -26007000 *MUL d.reg,s1.reg,s2.reg -28007000 *DIV d.reg,s1.reg,s2.reg -2a007000 *TRSA d.reg,s1.reg -2c007000 *TRSB d.reg,s2.reg -2e007000 *AND d.reg,s1.reg,s2.reg -30007000 *OR d.reg,s1.reg,s2.reg -32007000 *NAND d.reg,s1.reg,s2.reg -34007000 *NOR d.reg,s1.reg,s2.reg -36007000 *XOR d.reg,s1.reg,s2.reg -38007000 *XNOR d.reg,s1.reg,s2.reg -3a007000 *NOT d.reg,s1.reg -3c007000 *CMP reg1,reg2 -3e002000

Indirect addressing MODE IR Register : ROM- address Destination_REG Source_REG1 Source_REG2 8bit 8bit 3bit 5 bit 3bit 5 bit 5 bit 3bit 3bit 5 bit 5 bit Instructions : *IDSTOWE address - 2c102000 *IDSTOWO address - 2c142000 *IDSTODW address - 2c302000 *IDLODWE address - 2c187000 *IDLODWO address - 2c1c7000 *IDLODDW address - 2c387000

MEMORY MODE IR Register : REG-address IMMEDIATE ROM- address 8bit 3bit 5 bit 16 bit Instructions : *LODDW reg,address -4c395000 *IPNT immediate -4c022000 *PUSHWE reg -4c102400 *PUSHWO reg -4c142400 *PUSHDW reg -4c302400 *POPWE reg -4c195600 *POPWO reg -4c1d5600 *POPDW reg -4c395600 *STOWE address,reg -4c102000 *STOWO address,reg -4c142000 *STODW address,reg -4c302000 *LODWE reg,address -4c195000 *LODWO reg,address -4c1d5000 *INC reg,immediate - 40007000 *DEC reg,immediate -44007000

B31,B30,B29 B28,B27,B26,B25 B24,B23,B22 B21,B20,B19,B18 B17 B16 B15 B14,B13,B12 B11 (1) (2) (3) (4) (5) (6) (7) (8) (9) 1) Select Mode : {B31: Immediate mode , B30: Memory Mode , B29 : Register-Register Mode} 2) Execution Control 3) Execution Conditional Control 4) Memory Control : {B21: BHE , B20:Select Memory , B19:Memory R/w , B18:Memory Even/Odd } 5) Select Write Back Block or TTY Block 6) Select The Input of the Write Back Block From Alu Result or Memory Output 7) No Operation 8) Register File Control { B14:Write Register , B13:OE Register ,B12:Enabel Write Select Register } 9) Invert Condition

For Example • Executing These Two Instruction Sequentially • I1:R1=R2+R3 • I2:R4=R2 AND R1

l1 l2

l1 l2

l1 l2

l1 l2 Data Stored In R1

Solution • I1:R1=R2+R3 • NOP • NOP • NOP • I2:R4=R2 AND R1

L1 NOP

NOP NOP L1

NOP NOP NOP L1

L1 L2 NOP NOP NOP Data Stored In R1

L2 NOP NOP NOP

L2 NOP NOP

L2 NOP

Cisc Vs Risc Cisc: -Richer instruction set but very complex circuit. -Instructions generally take more than 1 clock to execute. -Instructions of a variable size. Risc: -Instructions execute in one clock cycle. -Uniformed length instructions and fixed instruction format. -Simple instructions and circuit.

Speed: With Pipelining: Each stage takes 4 clock cycles 5 stages IF,ID,EX,MEM,WB If clock rate 5 MHz then time for performing an instruction per pipeline stage is 0.8 µsec. Without Pipelining: If clock rate 5 MHz then time for performing an instruction is 4 µsec.

If ID MOV r1,05hMOV r2,04hADD r3,r1,r2STODW r3,1234h If ID If ID EX MEM WB If NOP NOP NOP ID EX MEM Pipelining

Average no. of stall cycles per instruction is 0.75Speed up is 2.85