Enhanced Cluster Processor Chip Design for High-Speed Data Capture and Processing

E N D

Presentation Transcript

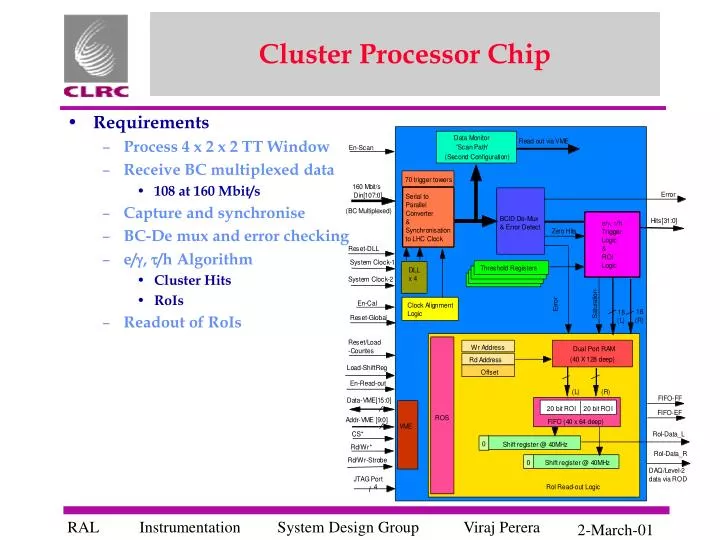

Cluster Processor Chip • Requirements • Process 4 x 2 x 2 TT Window • Receive BC multiplexed data • 108 at 160 Mbit/s • Capture and synchronise • BC-De mux and error checking • e/g, t/h Algorithm • Cluster Hits • RoIs • Readout of RoIs

Cluster Processor Chip • Requirements • Set-up and diagnostic Logic (second configuration)

Cluster Processor Chip • CP Chip Status • All logic blocks designed and integrated • Serial to Parallel conversion and Synchronisation • BCID De-multiplexing logic • Algorithm • Readout logic • Set-up and diagnostic logic implemented as a second configuration • More simulations to be done • Test vectors supplied by Steve Hillier

Cluster Processor Chip • Device • Fits in XCV1000E-6 • Latency • Seven, 40 MHz clock ticks (-6 device)