Advanced Digital Voice Processor Design for High-Quality Voice Applications

This project focuses on the design and implementation of a 16-bit Delta-Sigma Analog-to-Digital Converter (ADC) tailored for high-quality voice applications, including digital telephony, hearing aids, and VOIP systems. The design involves meticulous architectural planning, algorithm development, and rigorous testing of both digital and analog components. Key milestones include defining specifications, designing the schematic, and simulating components to ensure optimal performance. The layout reflects recent modifications to reduce size and complexity, ultimately achieving a highly efficient digital voice processing solution.

Advanced Digital Voice Processor Design for High-Quality Voice Applications

E N D

Presentation Transcript

TEAM W3:Digital Voice Processor 525 Jarrett Avery (W3-1) Sean Baker (W3-2) Huiyi Lim (W3-3) Sherif Morcos (W3-4) Amar Sharma (W3-5) Design Manager: Abhishek Jajoo Design Goal Date: 3/1/2006 Component Layout & Floorplan Design an Analog-to-Digital Conversion chip to meet demands of high quality voice applications such as: Digital Telephony, Digital Hearing Aids and VOIP.

Status • Design Proposal • Project chosen: 16 bit Delta-Sigma ADC • Basic specs defined • Architecture • Matlab simulated • Behavioral Verilog simulated • Structural Verilog simulated • Schematic • Digital – All modules created including top-level • Analog – All modules except modulator completed • Floorplan • Revised floorplan due to changes in design • Analog component sizes chosen and digital design completed • Simulation/Verification • All digital modules simulated and verified at top-level • Layout • Basic components (gates, full adder, flip-flop) completed • Sinc filter bit slice about 60% complete

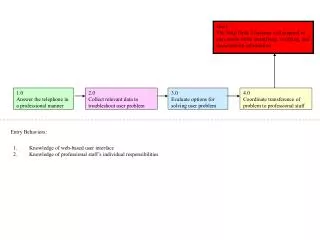

Algorithm Detail Analog Lowpass Filter Analog to Digital Conversion (Delta-Sigma Modulator) Decimation (Sinc Filter, Downsample) Analog Input Digital Output Measure Peak Amplitude (Peak Input Indicator) Digital Peak Indicator

Analog Design Progress • Optimized component sizes for low-pass filter and modulator • Low-pass filter schematic and layout completed • Op-amp transistor level schematic completed but in need of tuning

Algorithm Detail Digital Lowpass Filter Analog to Digital Conversion (Delta-Sigma Modulator) Decimation (Sinc Filter, Downsample) Analog Input Digital Output Measure Peak Amplitude (Peak Input Indicator) Digital Peak Indicator

Changes to Digital Design • Digital portion of design depends heavily on structure and topology of analog design • Analog design changed from 2nd order modulator to 1st order • Digital sinc filter must also change – from 3rd order to 2nd order • Adder and register widths must also change • width = order * log2(oversampling factor) = 2 * log2(256) = 2 * 8 = 16 bits • PII comparators and registers also reduced to 16-bit

Changes to Digital Design (cont’d) • Fixed problem relating to Nyquist clock • Added buffers to clean up signal • Changed Nyquist clock positive edge to occur on negative edge of oversampled clock • Changed full adder design to fix glitches occurring on sum outputs • Glitches caused by new inputs overlapping with old carry input due to slow carry out path • Original design used mirror adder with inverters on carry output • New design eliminates inverters through Boolean manipulations • Result is faster path through carry out and elimination of glitches on sum outputs

Changes to Full Adder • Mirror adder produces complemented carry and sum outputs • Invert inputs for every other bit & inverters for carry can be eliminated, reducing delay Diagram courtesy of Professor Ken Mai (ECE 722)

Top-level Schematic Simulation • Verified top-level digital module (i.e. decimator) against Verilog structural model using simulated analog input • Transistor level schematic simulated in Cadence Spectre • Analog output compared against structural digital outputs • Outputs match for both sinc filter and PII function sub-modules

Top-level Simulation (cont’d) • Simulated top-level module with analog behavioral model used earlier with behavioral Verilog models • Output is a digitized sine wave • This verifies the digital portion of our design at the transistor level

Critical Path • Our critical path located in sinc filter • Consists of two 16-bit subtracters connected in series • Critical path delay = 4.222 ns • Maximum clock frequency = 237 MHz • Speed is not an issue since we are operating at 5.12 MHz and 20 KHz • Area and power consumption much more important parameters

Layout of Basic Components • We have completed layout of some basic modules • Legacy layouts of primitive gates and 2-input mux • New layouts of flip-flop and full adder cells • Started bit slice of sinc filter module • Bit slice contains 4 full adders, 5 flip-flops, and some inverters • When finished, will stack 16 slices on top of each other to create 16-bit 2nd order sinc filter

Updated Floorplan • Major changes to design • Analog modulator changed to 1st order • Digital sinc filter changed to 2nd order • Adder and register widths changed to 16 bits • All these changes have reduced size of design considerably • Digital portion contains only 6,400 transistors • Analog portion contains 21 large transistors plus several extremely large (150 μm x 50 μm) resistors and capacitors

Problems and Questions • Simulating total design • Spectre/ModelSim comparison simulation took over 8 hours • AHDL mixed-signal simulation took 10 hours • How are we going to make changes and test them out? • Analog components still extremely large even for 1st order modulator • May cause overall area to exceed limit of 300,000 μm² • Layout of PII module • Less opportunities for bit slicing • Some large components – 24-bit counter • Use of GPDK design kit • Do we have to convert?